用DSP实现抖动(Jitter)测量的方法

近年来,抖动(Jitter)已经成为通信工程师非常重视的信号特征。在数字系统中,时钟频率正在变得越来越高。随着速率的升组,在上升沿或是下降沿哪性是微小的变化也变得越来越重要。因为时钟或数据的抖动会影响到数据的完整性、建立时间和保持时间。并且在考虑信号速率与传输距离之间的折中时,抖动也成为必须考虑的因素。

本文引用地址:https://www.eepw.com.cn/article/152190.htm抖动会使数字电路的传输性能恶化,由于信号上升沿或是下降沿在时间轴上的正确位置被取代,在数据再生的时候,数据比特流中就会引入错误。在合并了缓冲存储器和相位比较器的数字仪表中,由于数据溢出或是损耗,错误就会引入到数字信号中。此外,在数模变换电路中,时钟信号的相位调制会使恢复出的采样信号恶化,这在传输编码的宽带信号时会造成问题。

抖动分为系统抖动和随机抖动。

(1)系统抖动是在信号再生电路时间上不准,或是码是串扰,或是在幅频转换中的不准确的电缆均衡造成的。系统抖动取决于系统的性能。

(2)随机抖动来源于内部或是外部的干扰信号,如噪声、串扰、反射等。随机抖动与传输信号的系统无关。

系统抖动与不同的脉冲再生电路的脉冲的模式有关,会连续地积累。随机抖动则与脉冲再生电路的脉冲模式无关,而且也不会连续地积累;在大多数低速率的数字系统中,系统抖动占主导地位;而在高速系统中,随机抖动变得越来越重要,甚至会占据主导地位。

干扰性的抖动可以利用信号再生电路划中利用“去抖动”电路来减弱其影响。这种“去抖动”电路来减弱其影响。这种“去抖动”电路包括了一个带有窄带相位平滑电路的信号缓冲器。信号再生电路只能将抖动频率高于时钟再生电路的截止频率的抖动成分减小,而低频的抖动成分则仍然会出现在输出信号或是信号再生电路中。在这种情况下,抖动被传输到输出信号中,信号再生电路此时就象是一个低通滤波器。

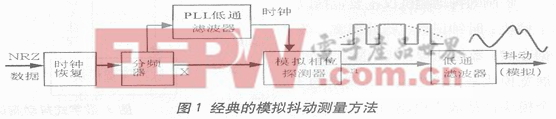

传统的抖动测量采用模拟测试的方法。图1给出了传统模拟测量方法的原理框图,它是将数据信号与基准时钟信号相比较,使用相位探测器的平均输出。模拟测量方法带来了很多问题,这都是因为相位探测器将相位表达成一个模拟电压引起的。

评论