用DSP实现抖动(Jitter)测量的方法

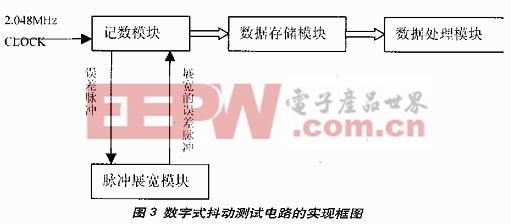

研制的抖动测试仪主要包括以下模块:时钟记数、脉冲展宽、数据存储、数据处理。其中除了脉冲展宽模块是模拟电路外,其余的3个模块都是数字电路,所以该设计是一种数字与模拟的混合电路。在设计中,考虑到算法的复杂性和灵活性,开发时间的紧迫性以及系统的要求,选用了德州仪器(TI)的TMS320F206。

TMS320F206是德州仪器公司用静态CMOS技术集成的DSP芯片,属于TMS320C2000系列。这是一种低功耗器件,采用了改进的哈佛结构,有1条程序总线和3条数据总线,有高度并行性的算术逻辑单元ALU、专用硬件逻辑、片内存储器、片内外设和高度专业化的指令集,从而使该芯片速度高、操作灵活。TMS320F206有224K的寻址能力、3个外部中断、1个同步串口和一个异步串口,最高时钟为40MHz。由于每秒需处理数据2Mbit,每个符号采样两次,所以实际数据速率是4Mbps。通过其算法来估计其运算量,40MIPS的处理能力完全可以满足其要求。在设计中使用了1个外部中断,一个异步串口。异步串口和PC机的串口相连接,将DSP计算结果送回到PC机显示。

时钟记数模块

该模块主要作用有以下几个:

①对二分频后的2MHz时钟信号用100MHz的时钟进行记数;

②用100MHz时钟对2MHz信号记数,产生误差脉冲;

③对展宽后的误差脉冲用100MHz的时钟进行记数;

④产生与数据存储模块接口的写时钟和写使能信号;

⑤将2MHz的记数值和展宽的误差脉冲记数值通过一路8位的数据总线分时输出。

此模块的设计主要是用一块XILINX公司的CPLD XC95108来完成的。

脉冲展宽模块

脉冲展宽模块是为了提高测试抖动的精度,这是本设计中非常关键的一个模块。本设计测试抖动其实就是精确地测试出每个周期的时间,只有测试的时间精度提高,最终测试抖动才能达到要求的精度。若无脉冲展宽电路,仅用100MHz的时钟记数的话,则单个周期的测时的最大误差将会是20ns,这样根本无法满足抖动测试的精度要求。

为了测出小于度量单位的一个物理量的值,我们很容易地想到只要将该物理量放大一个固定的倍数后,使该放大后的物理量可测,此时只要测出该物理量后除以该放大倍数,即可得到原先的物理量的值。该模块的设计就利用了这样的思路。具体是利用LM234产生两个恒流源,分别做为一个电容的充电电流和放电电流。利用充放电电流的不同产生斜率不同的充电曲线,再与一参考电压进行比较,即可得到一展宽的脉冲。具体的脉冲展宽电路是用两个三级管完成充放电工作和比较电路。三级管的型号是2SC3357,2SC3357是高频三级管,其工作频率可达到2GHz。选用高频三级管对此设计相当重要,因为要测的误差脉冲其时间只有几个ns。

数据存储模块

评论