FPGA单芯片四核二乘二取二的安全系统

引 言

二乘二取二系统的两套计算机系统各有两个CPU,并且所有结构和配件完全相同。两套系统之间采取双机热备份,大幅提高了系统可靠性,在一些领域得到了广泛应用。基于二乘二取二容错结构的计算机联锁系统在国外已有成熟的应用,如K5B和E132,其良好的可靠性和安全性引起国内业界的广泛关注。

系统可靠性冗余设计是提高系统可靠性的重要方法,但由于冗余会增加系统成本、体积和重量,因此必须合理地选择冗余结构和数量。对价格昂贵、重量大、体积大的冗余部分,更应作合理考虑。由于二乘二取二硬件冗余技术是通过多个相同部件完成同一功能,在提高系统可靠性的同时也存在一些不足:

◆增加了系统的成本、结构、重量和所需空间;

◆在某些情况下硬件技术的应用受到限制;

◆对大型复杂系统均采用硬件冗余技术是不可能的。

以上不足将限制二乘二取二冗余技术的应用,Fusion和coreABC的组合为以上问题提供了良好的解决方案。

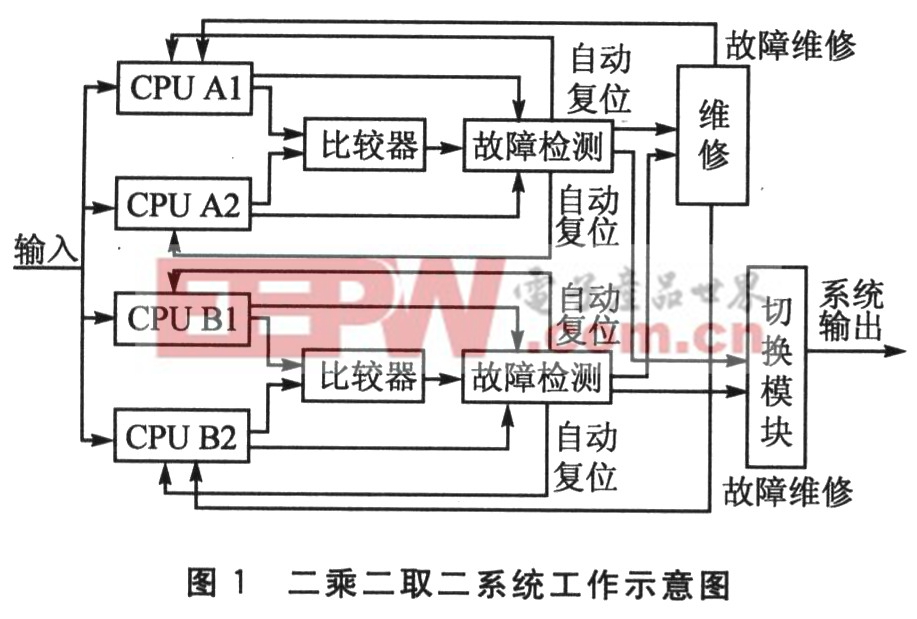

1 二乘二取二系统

二乘二取二系统有4个CPU,两个CPU组成一组。每两个CPU的输出经比较器表决输出,两个CPU和一个比较器表决系统组成一个子系统。两个子系统具有完全相同的硬件结构,一个为主单元,一个作为备用单元。开机后两个子系统独立同步工作,系统取工作单元的输出为系统输出。当两个子系统均正常工作时,系统取主单元的输出为系统输出,若备用单元发生故障,系统输出仍为主单元的输出,备用单元进入维修状态。当主单元发生故障时,系统切换至备用单元,此时系统输出为备用单元的输出,主单元进入维修状态;一旦主单元维修完毕,可以正常工作时,则系统切换至主单元,取主单元的输出为系统输出。若主单元和备用单元均无法正常工作,则系统故障,系统无法继续正常工作。除子系统故障时系统自动切换外,系统还具有手动切换的功能。由于两个子系统具有完全相同的结构和进行完全相同的工作,所以手动切换不影响系统的正常工作。导致系统故障的因素有很多,根据不同的应用场合,需要针对不同的故障进行检测和维修。二乘二取二系统的工作示意图如图1所示。

2 系统的具体实现

在设计时,首先要考虑FPGA门电路的数量,以及嵌入4个软核所要占用的门阵列资源。其次,要考虑其他硬件资源,比如时钟、存储器等。综合各方面的考虑,本设计选择Actel的Fusion StartKit数模混合FPGA实现二乘二取二系统。Fusion StartKit数模混合FPGA拥有600万门门阵列,片内集成了Flash存储器、RAM、FIFO和模拟模块;片外提供48 MHz的晶振;支持coreABC软核的嵌入。

2.1 软核的嵌入

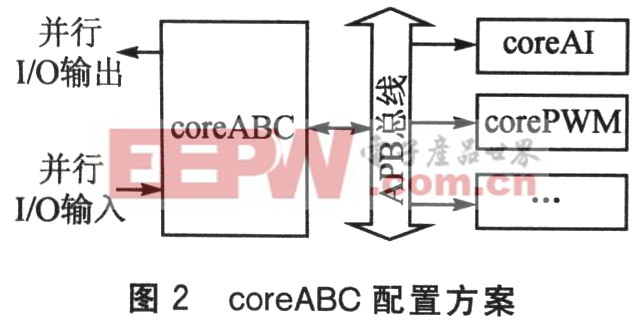

coreABC是一种具有高可配置性的软核,占用资源少,特别适于低端应用。它能够挂载可编程高级外围总线(APB),支持APB总线下的外围设备,通过coreAI直接控制ACM块,还可配置8位、16位和32位APB接口。可以通过APB总线控制coreAI核,进行电压、电流采集,以及模数转换。图2给出一种配置方案。coreABC可使用软/硬代码存储方式,本设计采用硬代码存储方式。硬代码存储方式只需占用门阵列资源,而软代码存储方式要占用Flash存储口资源。由于FPGA片内集成了2个Flash存储口,嵌入4个核时Flash存储口资源不足。Actel coreABC的推出对实现可配置的小系统极具意义,它使用很少的系统资源就可搭建起完整的控制单元。

2.2 比较电路的实现

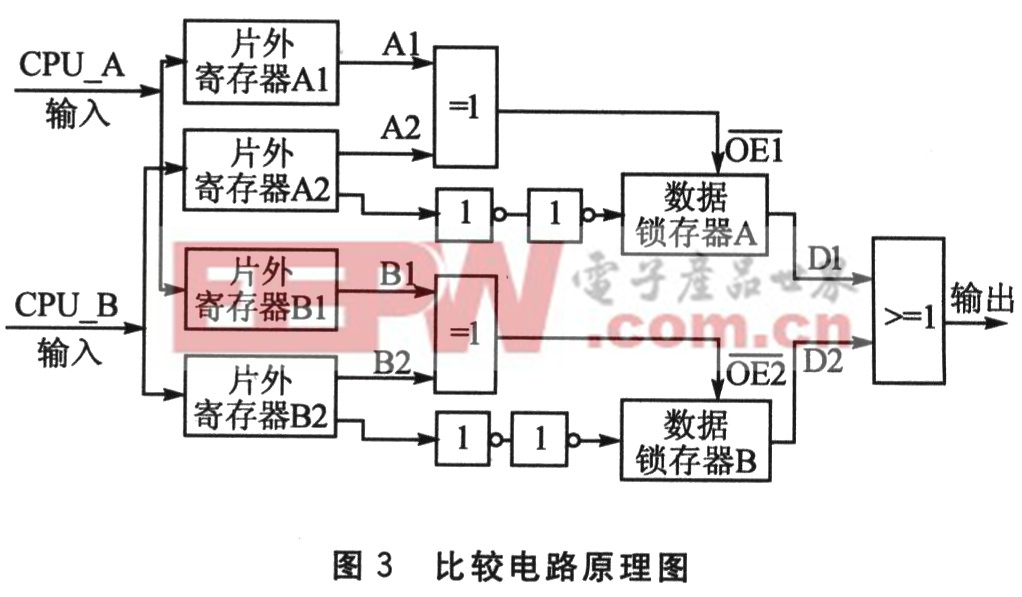

二取二CPU的比较电路采用冗余设计,它主要负责对coreABC软核的总线信号进行比较判决,保证系统正常运行,其电路图如图3所示。比较电路的工作原理为:片外寄存器分别从两个CPU获得总线数据信息,经异或模块OE1=A1+A2,OE2=B1+82进行判断,分别控制数据锁存器输出,并配合时钟信号控制锁存器同步输出;从锁存器输出的数据经或电路处理后形成比较结果,即DATA_OUT=D1+D2。若比较结果确认CPU此次运算一致,则系统正常输出;若比较电路确认CPU运算有误,则重新进行运算。

评论