采用JTAG仿真器的DSP中断检测处理技术方案

1、引言

4、DSP/BIOS 应用及实时性分析

本文引用地址:https://www.eepw.com.cn/article/152005.htm4.1 DSP/ BIOS的分析特性:

程序跟踪:显示写入目标日志的事件并在程序执行过程忠反映动态控制流程。

性能监控:跟踪、统计目标板资源的使用情况。

文件流:将目标板上的 I/O对象与主机上的文件联系在一起。其中: 1)DSP/ BIOS==Statistics View 统计表用于对程序的执行周期进行统计。

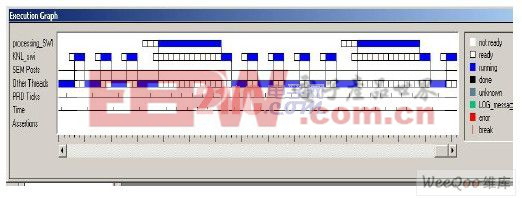

2)DSP/BIOS==Execution Graph 执行图以图示方式来反映程序执行时各进程间的配合,以分析程序执行的实时性。

3)DSP/BIOS==RTA Control Panel 控制仪表可以实时调整信息搜集和由此造成的对 CPU的干扰之间,通过禁止不同的隐式仪表类型,用户会丢失一些信息来换取减少开销。

4)DSP/ BIOS==CPU Load Graph ,CPU负荷图窗口,CPU活动分为两部分:工作时间和 IDLE时间。即 CPU负荷定义为执行一个应用程序时,CPU花费的指令周期数的百分比。

4.2 DSP/BIOS 实时性分析

一 )连接硬件,首先给 DSP目标扳加电,指示灯亮。

一 CCS运行环境。

一 )建立新项目,并在项目中添加相关文件。

一 )选择Project 菜单中 open选项,在弹出的对话框中选择编译工程*.cmd。

一 )选择Project 菜单中 Rebuild All选项,编译链接该工程,没有错误后,选择 File菜单中 Load Program选项,选择文件,进行加载程序。

一 )选择DSP/BIOS 菜单中CPU Load Graph , Execution Graph , Statistics View ,RTA Control Panel , Message Log 选项。

一 RTA Control Panel Properties 对话框,将 CPU Load Graph 改为 Every 0.5 Seconds 。[5]

一 )执行程序,执行图窗口如图3下:

如图3 执行图窗口

1 )连接硬件,首先给 DSP目标扳加电,指示灯亮。

2 CCS运行环境。

3 )建立新项目,并在项目中添加相关文件。

4 )选择Project 菜单中open选项,在弹出的对话框中选择编译工程。

5 )选择Project 菜单中 Rebuild All选项,编译链接该工程,没有错误后,选择 File菜单中 Load Program选项,选择文件,进行加载程序。

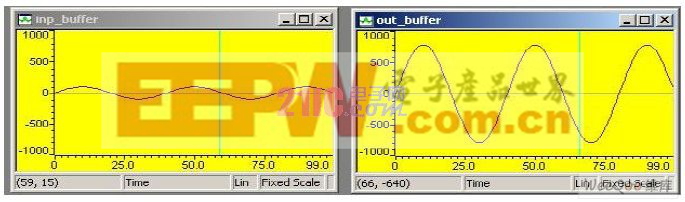

6 )选择File菜单中File I/O 选项,在对话框中Address 输入为Inp_buffer ,Legth为 100 ,进行链接,加载程序。

7 )将光标移至设定行 data IO ( ),设置中断点和探测点,选择 Debug菜单中 Breakpoints选项和 Probe Points 选项。

8 )选择View菜单中Watch Windows 选项和graph 选项,在graph 选项中 Time /Frequency选项中设置输入图形属性,设 Start Address 为inp_buffer ,Graph Title 为 inp_buffer ,Acquisition Buffer Size为 100,Display Data Size 为 100 , Maximum Y_Value 为 1000 , Autoscale为 off ,同时设置输出波形的属性。[4]

9 )执行程序,观察输入输出波形。如图4:

6、结束语

文章讨论了运用 JTAG仿真器在 CCS软件平台下对 TMS320 C54x系列 DSP芯片实现在线编程,在线调试时中断检测的处理,这样基于 JTAG仿真器的 DSP中断检测处理技术可以满足实时性分析的一些需求,提高了研究分析的精确性和针对性。但如果信号的测量需要更高精度、长时间的校准分析、更高性能的结果,最好选用嵌入式的仿真器及其相关专有的软件。

在采用集成化的开发调试平台CCS结合基于JTAG技术的仿真器实现 DSP系统的实时性分析过程中设定中断检测点是非常重要的,中断检测点可以中断程序的执行以进行特定的操作,例如可以进行数据文件的输入输出,可以刷新图表和数据窗口等,便于在实时性分析中更有效的观察数据处理的显示结果。

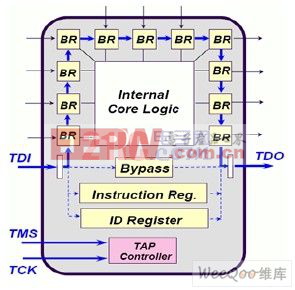

2、基于 JTAG技术的仿真器

JTAG技术即边界扫描技术,是一种专用的电子系统测试技术,就是通常所指的 IEEE1149.1标准,已经在各行业中得到了广泛的应用,如图 1,一个符合 IEEE1149.1标准的 JTAG器件,有别于不同的逻辑器件,内部都包括一个 TAP(测试访问端口)控制器,其次在芯片内部经由一个扫描链路将所有的输入和输出管脚全部串入一个扫描链路。

图 1 JTAG器件

基于 IEEE1149.1标准的边界扫描技术最先应用于大规模集成电路以及系统级芯片设计的 DFT技术,不仅可以保证集成电路芯片的外围管脚部分逻辑的正确,同时也对于嵌入在芯片内部的自测试机制等起到整合和控制等方面的作用。其次,通过芯片的 JTAG接口可以实现包括 FPGA、DSP以及处理器等在内的集成电路芯片的在线编程,同时也可以实现芯片的在线调试,前者是应用这一模式实现设计的下载,后者利用虚拟在线调试技术就是将芯片运行过程中部分的内部逻辑信息透过 JTAG接口传送到计算机中进行分析和判读。第三,基于 JTAG标准的边界扫描技术可以应用在印刷电路板的连通性测试领域,通过将 JTAG器件的边界扫描链连接在一起,并且控制合适的数据信息在该扫描链中传递,从扫描链的输出端进行监控就可以判别有关印刷电路板连通性以及元器件功能等方面的问题。

基于 JTAG技术的仿真器是用来进行芯片硬件仿真,如程序单步执行、设置中断检测点等,通过硬件仿真可以了解芯片里面程序的详细运行情况。 JTAG仿真器主要用来对芯片进行仿真操作,同时也可以通过 JTAG接口对芯片编程(将程序写入芯片)。它的接口方式有LPT(并行)口,PCI或ISA卡,USB口。JTAG仿真器一端通过USB口与PC机连接, 另一端通过 JTAG插头与 DSP目标板连接;建议首先连接 JTAG仿真器到 PC机, 再连接到 DSP目标板。[8] 3、基于 TMS320 C54XDSP芯片的信号发生器

3.1 TMS320 C54x系列 DSP芯片

TMS320 C54x系列 DSP芯片是使用静态 CMOS技术制造的。该芯片采用改进哈佛结构,对程序内存和数据内存使用分离的总线;可以同时取指令和操作数,提高了运行效率和通用性先进的 CPU设计和为应用设计的硬件逻辑提高了芯片的性能;为快速的后续发展设计了模块化的结构;为先进的 IC处理技术提供了高性能和低功耗;高度专门的指令结构提供了快速运算和优化的高阶语言操作;具有单指令循环和块指令循环功能;块内存移动指令提供了更好的程序和数据管理;拥有两个或三个操作数读取能力的指令;从中断快速返回的指令拥有多种片上外设和内存配置方案等特点。

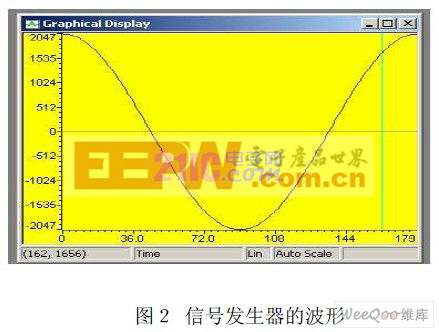

3.2信号发生器

一 )连接硬件,首先给 DSP目标扳加电,指示灯亮。

一 CCS运行环境。

一 )建立新项目,并在项目中添加相关文件。

一 Project 菜单中 open选项,在弹出的对话框中选择信号发生器的编译工程。

一 Project 菜单中 Rebuild All选项,编译链接该工程,没有错误后,选择 File菜单中 Load Program选项,选择 *.C文件,进行加载程序。选择 View菜单中 graph选项中 Time/Frequency设置图形属性,选择 Start Address 为 dacdata ,设 Acquisition Buffer Size为 180 ,设 Display Data Size为180 ,设 Dsp Data Type为 16-bit signed integer。点击 OK ,观察信号发生器的波形,如图2:

评论