System C特点及FPGA设计

一、概述

SYSTEM C 是由 Synospy Inc. 提出的,目前最新的版本为V2.0。它提出的目的就是以一种系统设计的思想进行系统设计。它将软件算法与硬件实现很好的结合在一起,提高了整个系统设计的效率和正确性。

System C 是一个C++ 库,也是一种使设计者可以有效地设计出一个软件算法的准确循环模型,硬件结构以及系统级设计的方法。 设计者可以用System C开发工具或在标准C++开发工具中加如System C库制作系统级模型,快速地仿真和优化设计,以及研究不同的算法,并且为硬件和软件设计人员提供一个设计系统的可执行规范。可执行规范本质上是一个C++程序,它显示了和设计系统同样的性能,为软件设计人员和硬件设计人员提供了一个设计的标准。

System C 库提供了创造系统结构模型的必须结构,包括那些在C++没有的功能如硬件时序,并行和触发功能。C++这种面对象语言提供了通过增加类来扩展语言的能力,而这种能力是C语言所不具备的。因此,System C使用大家熟悉的C++语言和开发工具。

二、SYSTEM C的特点

System C 支持对硬件和软件的联合设计,支持描述一个既包含硬件部分也包含软件部分的复杂系统结构。它也支持对接口的描述,有以下几个显著的特点:

1.System C可以为软件设计人员和硬件设计人员提供一个系统的可执行规范。设计人员使用该可执行规范可以避免设计中矛盾和错误的产生,并确保设计的完备性。这是应为在设计可执行规范时,系统设计者必须设计出也一个和系统具有同样工作状态的程序,通过这个程序可以发掘出潜在的矛盾和错误,并将这些矛盾和错误消除在整个设计的开始阶段,而不是在整个系统进行调试阶段才发现和解决这些矛盾和错误。这个程序还可以帮助设计者确保整个系统设计的完备性。

2.设计人员利用这个可执行的系统规范,还可以发现设计中概念模糊的地方。无论什么时候,设计人员对设计产生疑惑,就可以运行这个可执行程序以明确在这个问题上系统设计人员是如何处理的,从而确保系统设计的正确性。而现在的设计方法不能使设计人员方便迅速的解决这些疑惑。甚至这些疑惑是系统设计人员也不曾考虑过,这可能导致系统要重新进行设计。

3.在系统设计被实现以前,设计人员还可以通过用System C设计的系统可执行规范来验证整个系统设计。这样可以避免由于在系统设计上的失误,而使系统实现不能达到要求。现在的设计方法不能提供这样的手段在设计完成前进行系统的验证,对系统的验证必须是在系统设计完后。即使在完成前进行验证,由于不能完全模拟实际系统的工作,其结果也只能作为一种参考。

4.System C设计的可执行规范所使用的TESTBENCH文件可以通过小范围的修改或直接用在实现后的系统仿真。这就为设计实现人员带来很大的好处,他们不必花很多的时间去编写用来验证实现后系统正确性的TESTBENCH文件。而现在采用的设计方法所使用的TESTBENCH文件却没有提供这样的便利条件。这是应为软件设计人员和硬件设计人员两者的设计思想和设计手段都是不同的,一个软件设计人员所使用的TESTBENCH文件并不能被硬件设计人员使用,甚至不能给硬件设计人员任何帮助。

三、SYSTEM C设计与传统设计比较

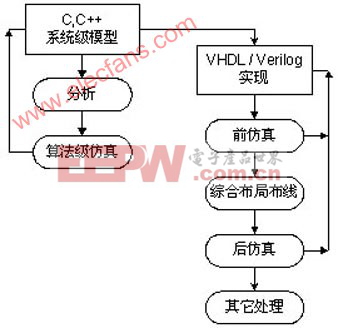

现在的系统设计一般是由系统工程师用C语言或C++语言设计出一个系统模型,并在系统级层次上检验概念和算法。当这些概念和算法被检验为正确无误时,C/C++模块被分解为功能相对独立的子模块。这些相对对立的子模块由硬件设计人员手工地转化为VHDL或Verilog语言用以硬件实现。这一个设计流程被显示在图1中。

图1

从图1所示的设计流程中我们可以发现以下几个问题:

1.人工将CC++程序转换为HDL程序容易产生错误。在现在的这种设计方法中,系统工程师先按期望的设计要求设计出一个C模块,并验证这个模块使其达到期望的设计要求。然后系统工程师所设计的C模块被硬件设计人员手工转换为HDL模块。这个转换过程不仅容易产生错误,而且还很浪费时间。这是因为CC++语言和HDL语言有着显著的区别。首先,HDL的处理方式比CC++的复杂。CC++程序采用顺序执行的处理方式,而HDL程序中既有顺序执行也有并行执行的处理方式。要将CC++程序转化为HDL程序必然要引入一些控制信号,由这些信号控制HDL程序的运行,但这样也容易产生错误。其次,CC++语言不涉及到时序关系。由于CC++语言不支持对时序的描述,系统工程师设计的系统模型只是验证了概念和算法,而只能对时间耗费上有一个大概的估计。这就使得硬件实现时,为满足系统在时间上的要求,硬件设计人员必须对软件算法进行一定的改造或优化。而这些改造或优化也有可能引入各种错误。

2.系统模块和HDL模块间缺乏联系。当系统模块被转换为HDL模块后,HDL模块成为整个系统设计的焦点。为适应硬件实现的特点,硬件设计人员会更改系统设计人员的设计,但这种更改只是在HDL模块中进行,而系统设计人员设计的C模块并没有因此更改。这就使得系统工程师设计的C模块和当前硬件设计人员设计的HDL模块缺乏必要的联系。当硬件设计人

员遇到概念模糊或理解错误的地方时,往往不能马上从C模块中得到明确的解答。此时,C模块的设计人员也不一定能为HDL设计人员提供有效的帮助。

评论