AD9850实现嵌入式信号源设计

引 言

本文引用地址:https://www.eepw.com.cn/article/150203.htm 信号源是现代电子系统的重要组成部分,在通信、测控、导航、雷达、医疗等领域有着广泛的应用,而且信号源作为现代电子产品设计和生产中的重要工具,必须满足高精度、高速度、高分辨率、频率可调等要求。

该设计采用直接数字频率合成(DDS)技术,使用DDS芯片AD9850与超低功耗的MSP430F149单片机配合,可输出精确控制的正弦波和方波信号。在控制流程中,通过4x 4矩阵键盘设定频率值,MSP430为AD9850计算频率控制字,并且将频率控制字通过串行方式写入其中,结合键盘上步进调节增量“1 Hz”,“10 Hz”,“100 Hz”键,使得频率可以精确到步长为1 Hz的调节;产生正弦波时,经过低通滤波器滤除信号的高频分量,通过增益可调的宽带放大器放大输出所需信号。如果接到AD9850内部的高速比较器上,即可直接输出一个抖动很小的方波,系统通过字符型液晶屏1602显示设定频率和其他信息。实验结果显示,输出信号频率范围在1 Hz~10 MHz,且无明显失真;输出信号频率实现1 Hz,10 Hz,100 Hz三级步进调节,频率精度0.01 Hz,频率转换速度1 ms,输出幅度范围1~10 V。

该设计的创新点在于:将DDS芯片AD9850与超低功耗的MSP430F149单片机结合,提出了具有较高性价比和集成度、低功耗的嵌入式信号源设计方案;并且AD9850与MSP430F149采用串行连接方式,节省单片机的I/O资源,便于系统的功能扩展和产品升级。该信号源具有精度高,频率范围宽,频率输出稳定,体积小,功耗低,控制灵活方便的特点,可广泛应用于日常教学和科研工作中,如果再经过结构优化,将具有良好的市场前景。

1 系统设计

1.1 DDS技术原理与结构

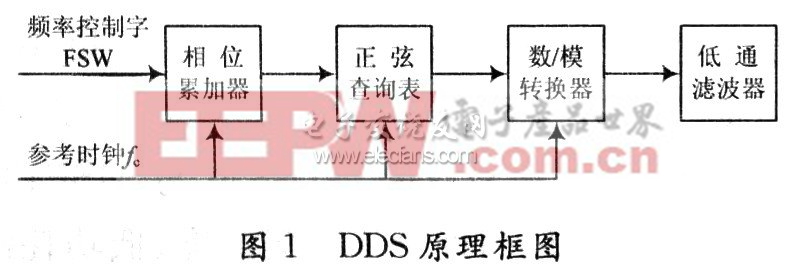

DDS技术是一种用数字控制信号的相位增量技术,具有频率分辨率高,稳定性好,可灵活产生多种信号的优点。一个DDS信号发生器由相位累加器、波形数ROM表、D/A转换器以及模拟低通滤波器LPF组成,原理框图如图1所示。DDS技术的核心是相位累加器。相位累加器在稳定时钟信号的控制下产生读取数据的地址值,随后通过查表变换,地址值被转化为信号波形的数字幅度序列,再由数/模变换器(D/A)将代表波形幅度的数字序列转化为模拟电压;最后经由低通滤波器将D/A输出的阶梯状波形平滑为所需的连续波形。DDS信号发生器通过改变相位增量寄存器的值△phase(每个时钟周期的度数)来改变输出频率。每当N位全加器的输出锁存器接收到一个时钟脉冲时,锁存在相位增量寄存器中的频率控制字就与N位全加器的输出相加。在相位累加器的输出被锁存后,它就作为波形存储器的一个寻址地址,该地址对应波形存储器中的内容就是一个波形合成点的幅度值,然后经D/A转换变成模拟值输出。当下一个时钟到来时,相位累加器的输出又加一次频率控制字,使波形存储器的地址处于所合成波形的下一个幅值点上。最终,相位累加器检索到足够的点就构成了整个波形。合成信号的波形取决于ROM表中的幅度序列,通过修改数据可以产生任意波形,如果要产生多种波形,只需把所需的多种波形数据存放到波形ROM表中。

DDS系统输出正弦波的频率计算公式为:

式中:fo为输出正弦波的频率;fo为系统的时钟频率;FSW为频率控制字;N为相位累加器的字长,频率控制字与输出频率成正比。由取样定理,所产生的信号频率能超过时钟频率的50 %,在实际应用中,为了保证信号的输出质量,输出频率不要高于时钟频率的33 %,以避免混叠或谐波落入有用输出频带内。

DDS的频率分辨率定义为:

由于基准时钟的频率一般固定,因此相位累加器的位数决定了频率分辨率;位数越多,分辨率越高。

该信号源采用DDS专用芯片AD9850产生正弦信号。AD9850采用CMOS工艺,其功耗在3.3 V供电时为155 mW,扩展工业级温度范围为-40~+80℃,采用28脚SSOP表面封装形式,AD9850内含可编程DDS系统和高速比较器,能实现全数字编程控制的频率合成。AD9850支持的时钟输入最高为125 MHz,频率控制字的位数为32位。由式(2)可以计算出在125 MHz时钟输入时分辨率为0.021 9 Hz,该设计中选用30 MHz的有源晶振,故其分辨率按式(2)计算得0.006 9 Hz。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论