基于DSP开发系统设计与实现

摘要:为了设计一个性能稳定的DSP开发系统,利用TI公司最新推出的TMS320F28335作为微处理器,该芯片为32位浮点型DSP。在采用浮点DSP设计系统时,不需要考虑处理的动态范围和精度,比定点DSP在软件编写方面更容易,更适合采用高级语言编程。外围电路主要包含电源电路、RAM扩展电路、晶振电路和复位电路,用来辅助DSP的工作。利用电源管理芯片设计电源电路,可以有效解决其他型号的DSP对上电顺序的要求;扩展的外部RAM可以使程序的调试与下载更加方便。利用外部时钟源作为时钟输入,使其输入时钟更加稳定的同时,也可为具有相同时钟的多个DSP使用。利用三端监控芯片来实现系统的手动复位和自动复位,使系统的稳定性大大提高。

关键词:TMS320F28335;浮点型;动态范围;数字信号处理器

TMS320F28335是TI公司最新推出的32位浮点型DSP,可直接参与浮点型数据的运算,无需Q格式的转换,其主要特点为:高性能的静态CMOS技术,在最高为150 MHz振荡频率下,指令周期为6.67 ns;高性能的32位CPU,单精度浮点运算单元(FPU),采用哈佛总线结构,能快速中断响应和处理,并有统一的存储器规划,可用C/C++语言实现复杂的算法;控制时钟系统具有片内振荡器和看门狗定时器模块,支持动态改变锁相环(PLL)的参数值以改变CPU的输入时钟频率;8个外部中断,相对于TMS320F281x系列DSP,无专门的中断引脚;支持58个外设中断的外设中断扩展寄存器(PIE),管理片上外设和外部引脚引起的中断请求;增强型的外设模块;12位A/D转换器,可实现16通道的数据转换;88个可编程的分时复用GPIO引脚;低功耗模式,1.9 V或1.8 V内核,3.3 V I/O供电。设计一个集这些优点于一身的DSP开发系统,对于初学者和开发人员有着重要的意义。本文首先分析和对比DSP电源设计方案,选择合适的设计方案并详细介绍;然后设计存储器扩展电路,并给出其存储范围;通过对比时钟电路的各种实现方案,择优选择适合于该系统的时钟电路并详细介绍;最后给出复位电路的设计方法和提高硬件抗干扰能力的措施。

1 系统电源设计

TI公司的DSP系列一般都有独立的内核和I/O电源。因为在DSP在系统中要承担大量的数据计算,在CPU内部,部件的高频率的转换会使系统功耗大大增加。所以采用双电源的供电方式,F28335一路为I/O提供3.3 V电压,另一路为CPU内核提供1.8 V或1.9 V电压,这样可大大降低系统的功耗。

电源设计方案一:两路电源独立没计,其优点是调试方便且互不干扰,缺点是不能适合某些对上电次序有要求的DSP,成本较高。

电源设计方案二:采用TI公司的双路低压差电压调整器。TPS767D3xx系列电压调整器是TI公司为DSP开发的电源管理芯片,通过简单的设计,可以适合某些系列DSP内核与I/O电压的上电顺序问题。

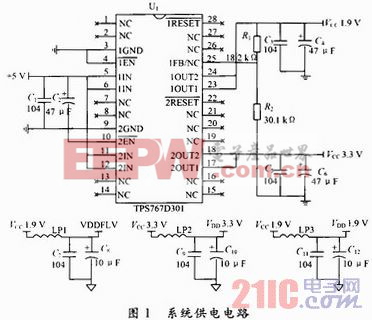

本设计采用方案二,利用TI公司的双路低压差电压调整器TPS767D301。它的特点是:带有可独立供电的双路输出,一路固定输出为3.3 V,另一路可以在1.5~5.5 V调整,每路输出电流范围为0~1 A;电压差大小与输出电流成正比,且在最大输出电流为1 A时,最大电压差仅为350 mA;超低的静态电流85μA,器件无状态时,静态电流仅为1μA。

TMS320F28335对内核和I/O的上电顺序没有要求,可以同时上电,使得电源电路大大简化。具体电路如图1所示。

评论