高清嵌入式系统中的DVI驱动开发

摘要:以飞思卡尔半导体的MX51为系统硬件平台,给出了高清嵌入式产品中DVI视频显示接口的实现方案;通过处理器的LCD1接口,外扩TFP 410芯片实现DVI视频输出;分析了framebuffer的实现机制及其在驱动中的应用;详细讲述Linux2.6.28内核下基于framebuffer开发DVI驱动的方法及步骤。该设计应用于高清机顸盒等产品中,效果良好。

关键词:Linux;设备驱动;DVI;framebuffer;MX51

引言

DVI是Digital VisualInterface(数字视频接口)的缩写。在嵌入式电子领域,像DVI这样的高清接口应用越来越多,很多嵌入式产品采用H.264视频编码技术,支持播放H.264格式的720P分辨率的视频文件,这就需要至少1024×768分辨率的显示输出设备。

MX51是飞思卡尔半导体的基于ARM Cortex-A8内核的高端ARM嵌入式多媒体处理器,支持720P视频多种格式的硬解码,可以用来开发高清机顶盒、上网本等产品,很多情况下需要集成DVI这样的高清视频端子。

在嵌入式电子产品中,Linux操作系统占有越来越多的市场份额。本文采用Linux2.6.28内核和MX51作为系统的软、硬件平台,详细论述了基于framebtffer技术开发DVI显示驱动程序的方法。

1 DVI概述

DVI接口只在一些高端显示器上可以看到,一般常见的液晶显示器只有VGA接口。VGA接口显示的是模拟信号,而DVI接口显示的是数字信号,它传输没有经过压缩的数字信号,最高速率可达4.9 Gbps,对高清视频显示可以达到较好的保真度,减少模拟信号传输时的信号损失。

DVI基于TMDS(Transition Minimized Differential Signaling,转换最小差分信号)技术来传输数字信号,TMDS运用先进的编码算法把8位数据(R、G、B中的每路基色信号)通过最小转换编码为10位数据(包含行场同步信息、时钟信息、数据DE、纠错等),经过DC平衡后,采用差分信号传输数据。DVI和LVDS、TTL相比有较好的电磁兼容性能,可以用低成本的专用电缆实现长距离、高质量的数字信号传输。

2 硬件接口

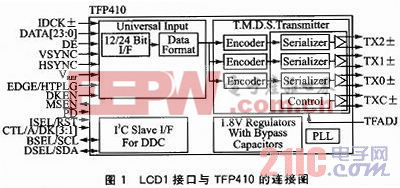

本设计采用的硬件平台是基于飞思卡尔半导体的MX51多媒体应用处理器开发板。该处理器集成了多种外设接口,其中包括两个液晶显示控制器(LCDC)及其接口,可以连接各类LCD,分辨率最大支持1280×800像素。通过MX51的LCD1接口,外扩德州仪器公司的TFP410芯片实现DVI视频输出,MX51的高清720P视频解码能力需要较大分辨率的显示输出设备。图1为MX51的LCD1接口与TFP410的连接图。

图1中的TX2±、TX1±、TX0±、TXC±信号是DVI视频输出信号4对,8个信号。DATA[23:0]是视频数据输入信号,对应MX51 LCD1的DATA[23:0];DE、VSYNC、HSYNC、IDCK±等时钟信号分别对应LCD1的相应的引脚。SCL、SDA是I2C总线时钟和数据信号,接MX51 I2C接口的2个引脚。以上硬件电路连接,可实现MX51输出高清视频到DVI芯片,再通过外接LCD显示。MX51处理器内部集成的LCD控制器包括如下主要寄存器:

①LSSAR寄存器。设置显示缓冲区的首地址。

②LSR寄存器。设置显示缓冲区的大小。

③LPCR寄存器。设置像素时钟频率PCD、同步时钟极性FB_SYNC_CLK_INVERT、OE信号极性FB_SYNC_OE_ACT_HIGH、垂直信号时钟极性FB_SY NC_VERT_HIGH_ACT、水平信号时钟极性FB_SYNC_HOR_HIGH_ACT。

④LHCR寄存器。设置行同步信号的hsync_len、left_margin和right_margin。

⑤LVCR寄存器。设置帧同步信号的vsync_len、upper_margin和lower_margin。

⑥LPCCR寄存器。设置屏幕的显示亮度,LPCCR的低8位控制PWM的脉冲高电平占空比,调节范围为0x00~0xFF。

评论