基于FPGA的时钟频率同步设计与应用

网络化运动控制是未来运动控制的发展趋势,随着高速加工技术的发展,对网络节点间的时间同步精度提出了更高的要求。如造纸机械,运行速度为1 500~1 800m/min,同步运行的电机之间1μs的时间同步误差将造成30 μm的运动误差。高速加工中心中加工速度为120 m/min时,伺服电机之间1μs的时间同步误差,将造成2 μm的加工误差,影响了加工精度的提高。

本文引用地址:https://www.eepw.com.cn/article/138517.htm分布式网络中节点的时钟通常是采用晶振+计数器的方式来实现,由于晶振本身的精度以及稳定性问题,造成了时间运行的误差。时钟同步通常是选定一个节点时钟作为主时钟,其他节点时钟作为从时钟。主节点周期性地通过报文将主时钟时间发送给从节点,从节点接收到报文后,以主时钟为基准进行延迟补偿,然后将计算出的新时钟值赋给从时钟。这种同步方法造成了从时钟计数值的不连续,即会出现重复(从时钟晶振频率快于主时钟)或跳跃(从时钟晶振频率慢于主时钟),而且这种方法并没有从根本上解决时钟频率的不同步问题,因此要进一步提高同步精度很困难。本文研究了一种可对频率进行动态调整的时钟,通过对时钟频率的动态修正,实现主从时钟频率的同步,进而实现时间同步。

1 时钟同步原理

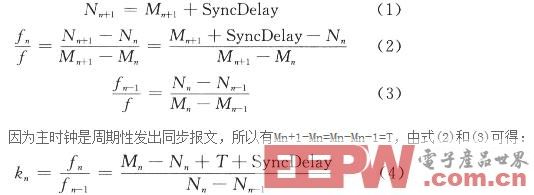

要实现两个时钟的同步,一是时钟的计数值要相同,二是计数增长速率要相同。如图1所示,设主时钟的频率为f,从时钟频率在Nn-1到Nn时间段为fn-1,在Nn到Nn+1为fn,SyncDelay为同步报文从主站到从站的延迟时间,可以通过延时测量帧采用往返法测量得到,从时钟要在Nn+1时刻达到与主时钟相等,那么有:

kn就是时钟频率调整系数。在每个同步周期可以计算出频率调整系数,然后通过相应的硬件电路来实现频率调节。

2 可调频率的时钟设计

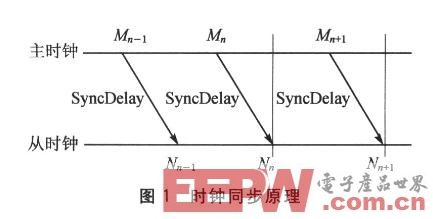

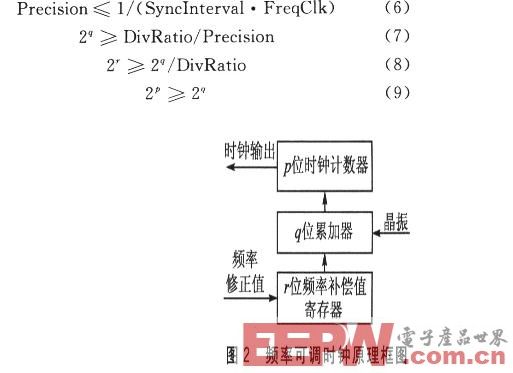

可调频率时钟是一种完全由数字电路组成的时钟计数器,构造简单,可以很方便地在FPGA中实现,原理如图2所示。该频率可调时钟由一个户位时钟计数器,q位累加器和r位频率补偿值寄存器组成。每个晶振周期,累加器与频率补偿寄存器中的FreqCompValue相加,并将结果保存到累加器。如果累加器发生溢出,时钟计数器的值就增加1;反之,时钟计数器保持不变。由此可以看出,晶振频率和频率补偿值FreqCompValue的大小决定了累加器的溢出速率,也决定了时钟计数器的计数频率。所以可以通过调整FreqCompValue来调节时钟频率。为了实现高精度时钟,晶振频率要比时钟频率高。设晶振频率为FreqOsc,时钟计数频率为FreqClk,分频比为DivRatio,同步周期为SyncInterval,补偿精度为Precision,p、q、r可由下列公式得出:

DivRatio=FreqOsc/FreqClk (5)

在本系统中,取FreqClk为50 MHz,FreqOsc为60MHz,则DivRatio为1.2。当同步周期为1 s时,补偿精度Precision可选10-9,由公式可选择r=q=32,p=64。频率补偿初值由下式求出:

FreqCompValue=2q/DivRatio=232/1.2=32d3579139413

在时钟输出算法中,该值由频率调整系数动态调整:

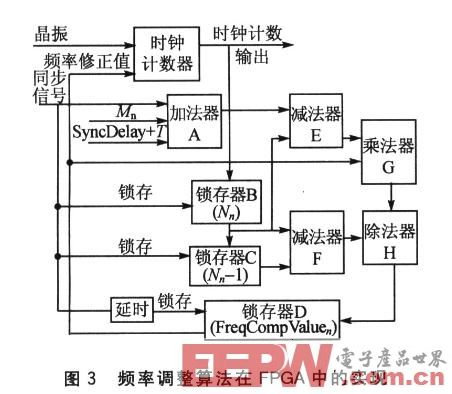

FreqCompValuen=kn·FreqCompValuen-1 (10)3 频率补偿算法在FPGA中的实现

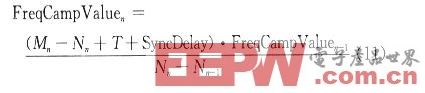

由式(4)和式(10)可得:

频率补偿就是在每个同步周期计算FreqCompValuen,FPGA提供了参数化的乘法器兆函数(1pm_mult)和除法器兆函数(1pm_divide),可以快速实现上述算法。原理如图3所示,在每个同步周期同步信号的驱使下,锁存器B和C分别锁存当前时钟读数和上个同步周期时钟读数,同时将主时钟读数输入到加法器A中,经过减法器E、F和乘法器G,以及除法器H后计算出新的FreqCompValuen,并在同步信号的驱动下,将其锁存到锁存器D中。由于中间的计算结果要经过一定的时钟周期,所以锁存器D的锁存信号要延时一定的晶振周期。在本设计中延时50个FreqOsc,即在<1μs的情况下就可以得到新的频率补偿值。

同步报文的传输延迟SyncDelay理论上是不变的,而实际上报文在传输过程中有抖动。参考文献[3]对此进行了分析,并指出同步周期越长,报文传输延迟抖动的影响就越小,因此可以忽略不计。

4 实验验证

主时钟采用50 MHz的有源晶振来实现,并将其作为固定时钟;从时钟采用30 MHz有源晶振,通过FPGA的锁相环PLL将其频率倍频到60 MHz,然后1.2分频,实现可调频率的50 MHz时钟。

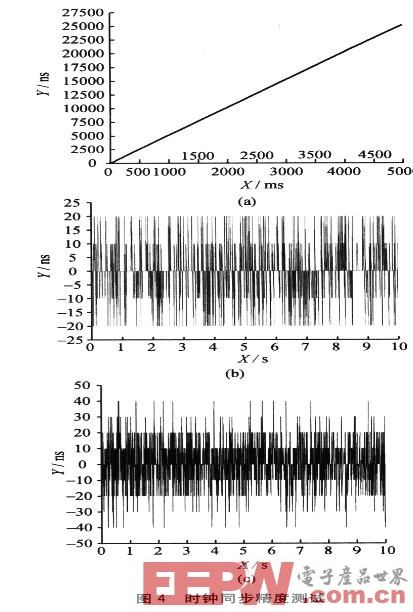

让主时钟和从时钟以一定的时间间隔产生中断,并通过逻辑分析仪采样中断信号分析其偏差。由于系统时钟的分辨率为20 ns,采用广州致远电子有限公司的逻辑分析仪LA1532,其最大采样频率为100 MHz,所以偏差测量精度可以达到10 ns。图4(a)是未进行同步前两个时钟的偏差分析,X轴表示主时钟和从时钟的计时长度,Y轴表示主时钟和从时钟的计时偏差。从图中可以看出两个时钟的偏差大概为5×10-6,即1 s内的偏差可以达到5μs。图4(b)为同步后主时钟和从时钟偏差测量结果,共测量1 000次,其10 ms内同步偏差在±20 ns。X轴表示测量时间,Y轴表示主从时钟同步偏差。图4(c)为同步后两个从时钟偏差测量结果,共测量1 000次,其10 ms内同步偏差在±40 ns。X轴表示测量时间,Y轴表示从时钟之间同步偏差。

结 语

基于时钟频率调整的时间同步方法,实现简单,而且没有复杂的软件同步协议,占用较小的网络带宽就可以实现高精度的时钟同步,在硬件上只需要低成本的FPGA支持。

fpga相关文章:fpga是什么

伺服电机相关文章:伺服电机工作原理

尘埃粒子计数器相关文章:尘埃粒子计数器原理 晶振相关文章:晶振原理 锁相环相关文章:锁相环原理

评论