一种高速I2C总线从器件接口IP核的设计与实现

引言

I2C总线作为一种事实上的国际标准,在超过100种不同的IC上实现并且得到超过50家公司的许可。它具有连线少,结构简单的特点。本文介绍了一种高速I2C从器件接口电路IP核设计。在系统应用中,单片机作为主控器件,本IP核作为从器件中的接口电路,它们通过I2C总线相连,实现MCU对IC或FPGA中相关寄存器的访问。从而代替了MCU通用的地址数据接口,大大减少了IC或FPGA的管脚数量,节省了I/O资源,这对于I/O资源紧张的IC设计和FPGA开发是非常有意义的。

I2C总线简介

I2C总线利用两条线SDA(串行数据线)和SCL(串行时钟线)完成总线上设备间的数据交换。出现过3个版本标准:1992年的v1.0、1998年的v2.0和2000年的v2.1。I2C总线支持串行的8位双向数据传输,传输速率在标准模式下可达100kbit/s,快速模式下可达400kbit/s,高速模式下可达3.4Mbit/s。包含四种工作模式:主机发送模式、主机接收模式、从机接收模式、从机发送模式。

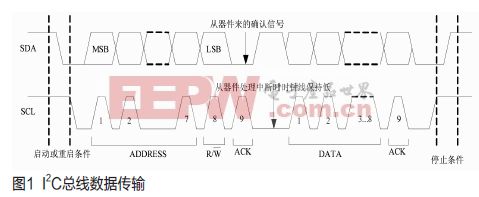

I2C定义了7位和10位两种从机地址的数据传输模式。一般的,7位地址模式应用比较广泛,其数据传输模式如图1所示。

从图1中可以看到,当时钟线SCL=1,数据线SDA从“1”变为“0”时,即表示出现了一个启动条件(或是重新启动条件)。其后是7位地址信号,第8位表示的是本次访问的类型(读/写),“0”表示写,“1”表示读。第9位是从器件的应答信号,“0”表示应答确认,“1”表示应答不被确认。之后数据以9位循环,前8位是数据第9位是从器件的应答位。当时钟线SCL=1,数据线SDA从“0”变为“1”时,既表示出现了一个停止条件。启动条件发生后开始数据传输,停止条件发生后表示本次数据传输结束。

评论