- 亮点: 设计规划速度提升了10倍,实现速度提升了5倍,容量提升了2倍 – 它们共同使吞吐量加速了10倍 构建于全新的可扩展基础架构、时序和解析优化引擎之上 已经在成熟和新兴的技术节点上成功生产流片 为加速芯片和电子系统创新而提供软件、知识产权(IP)及服务的全球性领先供应商新思科技公司日前宣布:正式推出将导致游戏规则发生改变的IC Compiler II,它是当前领先业界的布局和布线解决方案IC Compiler™的继任产品,可用于基于成熟和新

- 关键字:

Synopsys IC RTL

- 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS)日前宣布,已经达成了一项最终协议,收购以SystemC为基础的高阶综合(HLS)与算法IP供应商Forte Design Systems。

- 关键字:

Cadence SystemC RTL

- 电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

- 关键字:

数字硬件 RTL 参数测试 JTAG

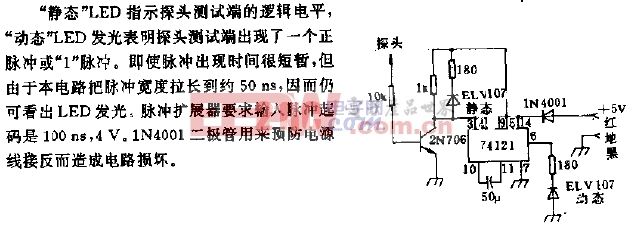

- 寄存器传输级(RTL)验证在数字硬件设计中仍是瓶颈。行业调研显示,功能验证占整个设计工作的70%。但即使把重点放在验证上面,仍有超过60%的设计出带需要返工。其主要原因是在功能验证过程中暴露出来的逻辑或功能瑕疵和

- 关键字:

RTL 时序逻辑 等效 检查方法

- 在系统级芯片设计中,设计验证是一项十分重要的工作。传统的验证方法虽然比较简单,但对设计工程师要求很高,而且验证时间过长。本文介绍开放式设计和验证语言SystemC,通过该语言可实现RTL测试平台的复用,降低验证

- 关键字:

RTL 测试平台 模型

- 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS),日前宣布推出最新版Cadence® Encounter® RTL-to-GDSII流程,面向高性能千兆级设计,包括在20纳米最新技术节点上的新设计。这种最新的RTL-to-GDSII设计、实现与签收流程是与领先的IP与晶圆厂合作伙伴及客户合作开发的,能更有效地进行SoC开发,满足并超越当今市场所需的功耗、性能与面积需求。

- 关键字:

Cadence RTL-to-GDSII

- 有限状态机及其设计技术是数字系统设计中的重要组成部分,是实现高效率、高可靠性逻辑控制的重要途径。大部分数字系统都可以划分为控制单元和数据单元两个组成部分。通常,控制单元的主体是一个状态机,它接收外部

- 关键字:

RTL 策略 方案

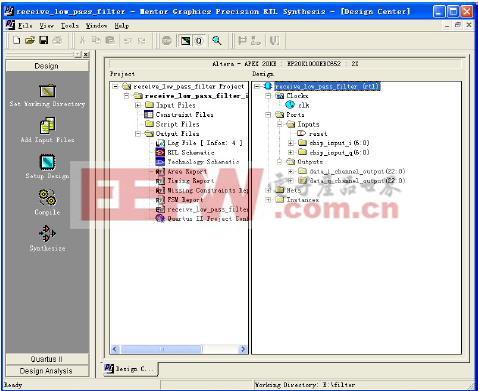

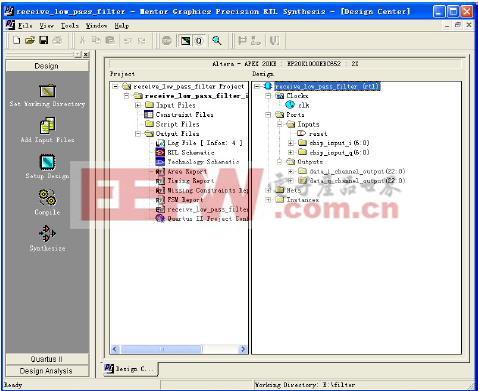

- 在FPGA设计中使用Precision RTL 综合实例,数字滤波器通常分成有限脉冲响应(finite impulse response,也就是FIR)和

无限脉冲响应(infinite impulse response,也就是IIR)两大类。FIR 滤波器相对

于IIR滤波器而言,优点是相位线性和性能稳定,应用范围广

- 关键字:

综合 实例 RTL Precision 设计 使用 FPGA

- Synopsys日前宣布,在其Galaxy设计实现平台中推出了最新的RTL综合工具Design Compiler 2010,它将综合和物理层实现流程增速了两倍。Design Compiler自1988年问世以来,随着工艺技术从1.5微米到32纳米的进步,而不断得到调整升级。而今时序与面积布线的优化已成为主要的挑战,最新版工具与时俱进,针对拓扑技术进行扩展,为Synopsys布局布线解决方案IC Compiler提供“物理层指引”;将时序和面积的一致性提升至5%的同时,还将IC

- 关键字:

Synopsys RTL 32纳米

- 全球领先的半导体设计、验证和制造的软件及知识产权(IP)供应商新思科技有限公司日前宣布:该公司在其Galaxy™设计实现平台中推出了最新的创新RTL综合工具Design Compiler 2010,它将综合和物理层实现流程增速了两倍。为了满足日益复杂的设计中极具挑战性的进度要求,工程师们需要一种RTL综合解决方案,使他们尽量减少重复工作并加速物理实现进程。为了应对这些挑战,Design Compiler 2010对拓扑技术进行扩展,为Synopsys旗舰布局布线解决方案IC Compile

- 关键字:

Synopsys Galaxy RTL

- 全球领先的半导体设计、验证和制造软件及知识产权(IP)供应商新思科技公司与中国内地最大的芯片代工企业中芯国际集成电路制造有限公司日前宣布,将携手推出全新的65纳米RTL-to-GDSII参考设计流程4.0(Reference Flow 4.0)。作为新思科技专业化服务部与中芯国际共同开发的成果,该参考流程中增加了 Synopsys Eclypse™ 低功耗解决方案及IC Compiler Zroute布线技术,为设计人员解决更精细工艺节点中遇到的低功耗和可制造性设计(DFM)等问题提供更多

- 关键字:

中芯国际 65纳米 Galaxy RTL-to-GDSII参考设计流程4.0

- 2004年12月在一项由Synplicity公司委托的调查中,全世界超过20,000名开发者被询问关于他们的硬件辅助ASIC验证...

- 关键字:

FPGA ASIC NRE RTL

- 美国加州圣荷塞 2009年4月14日– 芯片设计解决方案供应商微捷码(Magma®)设计自动化有限公司(纳斯达克代码:LAVA)日前宣布,该公司面向先进集成电路的全芯片综合产品Talus® Design的最新版本正式面市。新版Talus® Design包括了一个增强的时序优化引擎、改善的内存使用效率以及先进的生产率改进,比如:创新性可用性、更为灵活的先进脚本语言以及领先的第三方可测性设计(DFT)产品支持。同时,Talus Design与Talus Vortex相结

- 关键字:

Magma RTL DFT Talus

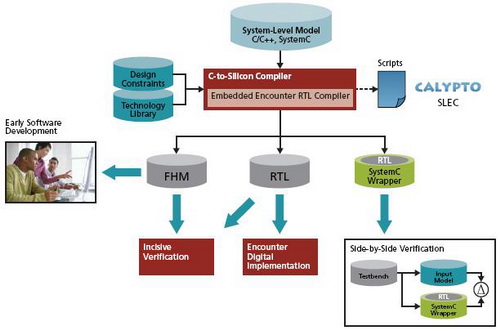

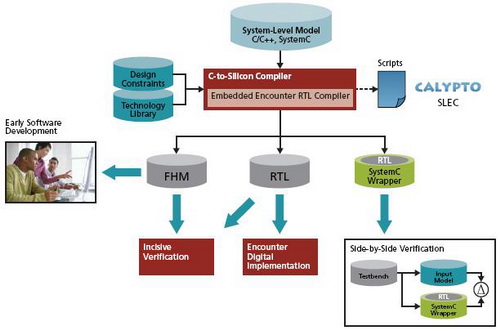

- 全球电子设计创新领先企业Cadence设计系统公司(纳斯达克: CDNS),今天宣布推出Cadence® C-to-Silicon Compiler,这是一种高阶综合产品,能够让设计师在创建和复用系统级芯片IP的过程中,将生产力提高10倍。C-to-Silicon Compiler中的创新技术成为沟通系统级模型之间的桥梁,它们通常是用C/C++ 和SystemC写成的,而寄存器传输级(RTL)模型通常被用于检验、实现和集成SoC。这种重要的新功能对于开发新型SoC和系统级IP,用于消费电子、无

- 关键字:

Cadence RTL SoC IP

- 全球电子设计创新企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布面向Common Platform™技术的45纳米参考流程将于2008年7月面向大众化推出。Cadence®与Common Platform技术公司包扩IBM、特许半导体制造公司和三星联合开发RTL-to-GDSII 45纳米流程,满足高级节点设计需要。该参考流程基于对应Common Power Format(CPF)的Cadence低功耗解决方案,而且还包含来自Cadence的关键可制造性设计(De

- 关键字:

CADENCE Common Platform ARM RTL-to-GDSII 低功耗

rtl介绍

RTL是Real Time Logistics的缩写, 意为:实时物流,是顺应新经济变革的当代物流理念,与现代物流理念区别在于,实时物流不仅关注物流系统成本,更关注整体商务系统的反应速度与价值;不仅是简单地追求生产、采购、营销系统中的物流管理与执行的协同与一体化运作,更强调的是与企业商务系统的融合,形成以供应链为核心的商务大系统中的物流反应与执行速度,使商流、信息流、物流、资金流四流合一,真正实现 [

查看详细 ]

- 如何读懂数字电路RTL设计?

- 深圳IC厂商诚聘资深数字IC设计工程师

- KEIL,RTL,HTTP,DEMO,EASYARM2200,nbsp,nbsp,WEB KEIL-RTL HTTP-DEMO EASYARM2200

- MSP430,RTL8019 MSP430+RTL8019(新手上路,多多指教)

- Keil,ARM,RV,RTL,KIT 急切寻找 Keil ARM RV-RTL KIT ???

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473