- Verilog HDL中,有两种过程赋值方式,即阻塞赋值(blocking)和非阻塞赋值(nonblocking)。阻塞赋值执行时,RHS(right hand statement)估值与更新LHS(left hand statement)值一次执行完成,计算完毕,立即更新。在执行时

- 关键字:

Verilog HDL 阻塞属性

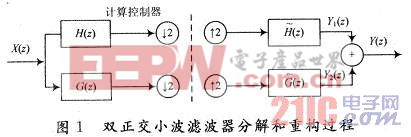

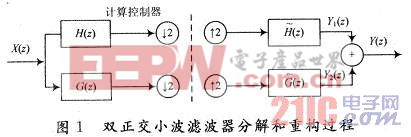

- 现代计算机和通信系统中广泛采用数字信号处理的技术和方法,其基本思路是先把信号用一系列的数字来表示,然后对这些数字信号进行各种快速的数学运算。其目的是多种多样的,有的是为了加密,有的是为了去掉噪声等无

- 关键字:

设计 滤波器 HDL Verilog 基于

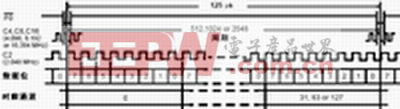

- ST-BUS总线接口模块的Verilog HDL设计,ST-BUS是广泛应用于E1通信设备内部的一种模块间通信总线。结合某专用通信系统E1接口转换板的设计,本文对ST-BUS总线进行了介绍,讨论了ST-BUS总线接口收发模块的设计方法,给出了Verilog HDL实现和模块的时序仿真图。

- 关键字:

HDL 设计 Verilog 模块 总线 接口 ST-BUS

- PLD/FPGA硬件语言设计verilog HDL,HDL概述 随着EDA技术的发展,使用硬件语言设计PLD/FPGA成为一种趋势。目前最主要的硬件描述语言是VHDL和verilog HDL及System Verilog。 VHDL发展的较早,语法严格;而Verilog HDL是在C语言的基础上发展起来的一种硬

- 关键字:

verilog HDL 设计 语言 硬件 PLD/FPGA

- Verilog HDL与VHDL及FPGA的比较分析, Verilog HDL 优点:类似C语言,上手容易,灵活。大小写敏感。在写激励和建模方面有优势。 缺点:很多错误在编译的时候不能被发现。 VHDL 优点:语法严谨,层次结构清晰。 缺点:熟悉时间长,不够灵

- 关键字:

比较 分析 FPGA VHDL HDL Verilog

- 摘要:通用异步收发器UART常用于微机和外设之间的数据交换,针对UART的特点,提出了一种基于Ver4log HDL的UART设计方法。采用自顶向下的设计路线,结合状态机的描述形式,使用硬件描述语言设计UART的顶层模块及各个子

- 关键字:

Verilog UART HDL 模块设计

- 基于FPGA和DDS的信号源设计,1 引言

直接数字频率合成DDS(Direct Digital Synthesizer)是基于奈奎斯特抽样定理理论和现代器件生产技术发展的一种新的频率合成技术。与第二代基于锁相环频率合成技术相比,DDS具有频率切换时间短、频率分辨率

- 关键字:

设计 信号源 DDS FPGA 基于 FPGA,DDS,Verilog HDL

- Altium继续在其下一代电子产品设计软件Altium Designer中提供新功能,帮助电子产品设计人员站在新科技和潮流的最前沿。

Altium公司首席执行官Nick Martin表示:“我们认为,让用户等待每隔数年才更新一次版本的产业模型已经完全不符合当前的需求。”

此次最重要的新特性是基于网络的软件许可证管理和访问选项。它使电子产品设计人员能够有效地管理设计团队、工作量及项目。

Altium Designer中的其他新特性包括针对板卡级设计人员的定制FP

- 关键字:

Altium 电子产品设计 FPGA HDL

- 直接数字频率合成技术(Direct Digital Synthesize,DDS)是继直接频率合成技术和锁相式频率合成技术之后的第三代频率合成技术。它采用全数字技术,并从相位角度出发进行频率合成。随着微电子技术和数字集成电路的飞速

- 关键字:

Verilog HDL DDS 仿真

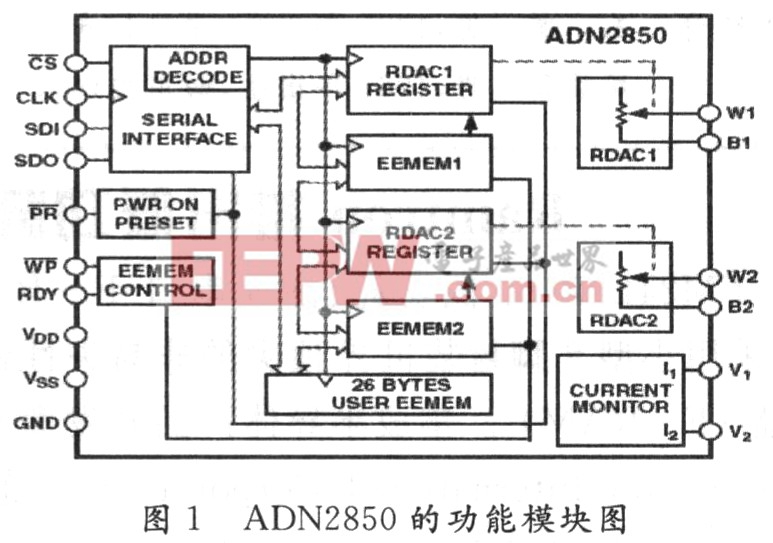

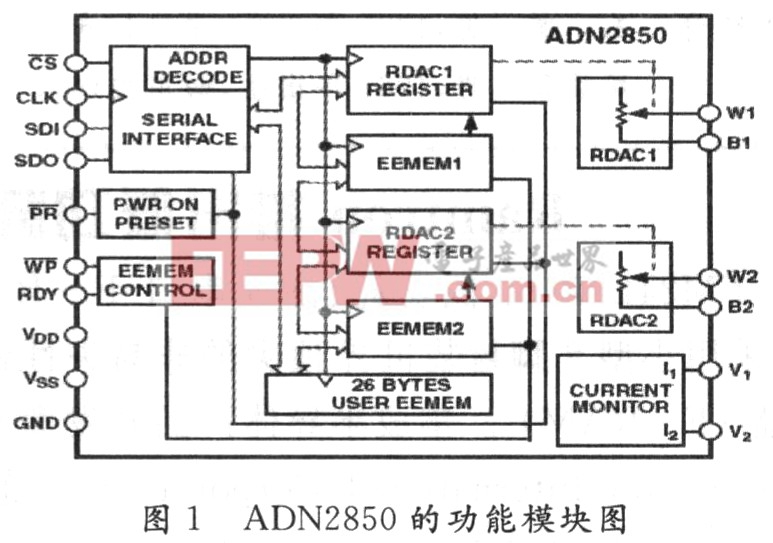

- 摘要:数字电位器由于可调精度高,更稳定,定位更准确,操作更方便,数据可长期保存和随时刷新等优点,在某些场合具有模拟电位器不可比拟的优势。论述对数字电位器ADN2850的一种方便的控制方法,通过计算机上的串口直

- 关键字:

串口 控制 ADN2850 数字电位器 Verilog HDL 基于

- 针对机器人伺服控制系统高速度、高精度的要求,介绍一种全数字化的基于神经网络控制的直流电机速度伺服控制系统的设计方案。速度控制器采用BP网络参数辨识自适应控制,并将其在FPGA进行硬件实现;同时用Nios II软核处理器作为上位机,构成一个完整的速度伺服控制器的片上可编程系统(SOPC)。实验结果表明,该控制系统具有较高的控制精度、较好的稳定性和灵活性。

- 关键字:

SOPC 系统 控制器 速度 神经网络 电机 基于 神经网络 伺服控制 现场可编程门阵列 Verilog HDL

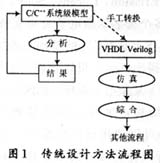

- 随着集成电路制造技术的迅速发展,SOC设计已经成为当今集成电路设计的发展方向。SO C设计的复杂性对集成电路设计的各个层次,特别是对系统级芯片设计层次,带来了新挑战,原有的HDL难以满足新的设计要求。

硬件设计领域有2种主要的设计语言:VHDL和Verilog HDL。而两种语言的标准不统一,导致软硬件设计工程师之间工作交流出现障碍,工作效率较低。因此,集成电路设计界一直在寻找一种能同时实现较高层次的软件和硬件描述的系统级设计语言。Synopsys公司与Coware公司针对各方对系统级设计语言的

- 关键字:

SOC SystemC 集成电路 VHDL Verilog HDL

hdl介绍

HDL(Hardware Description Language),是硬件描述语言。顾名思义,硬件描述语言就是指对硬件电路进行行为描述、寄存器传输描述或者结构化描述的一种新兴语言。

主流的HDL分为VHDL和Verilog HDL。VHDL诞生于1982年。在1987年底,VHDL被IEEE和美国国防部确认为标准硬件描述语言。自IEEE公布了VHDL的标准版本,IEEE- 1076(简称 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473