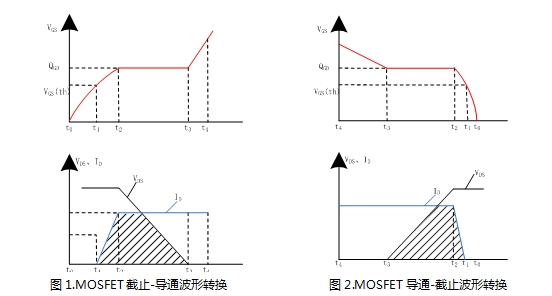

一、引言 MOSFET作为主要的开关功率器件之一,被大量应用于模块电源。了解MOSFET的损耗组成并对其分析,有利于优化MOSFET损耗,提高模块电源的功率;但是一味的减少MOSFET的损耗及其他方面的损耗,反而会引起更严重的EMI问题,导致整个系统不能稳定工作。所以需要在减少MOSFET的损耗的同时需要兼顾模块电源的EMI性能。 二、开关管MOSFET的功耗分析

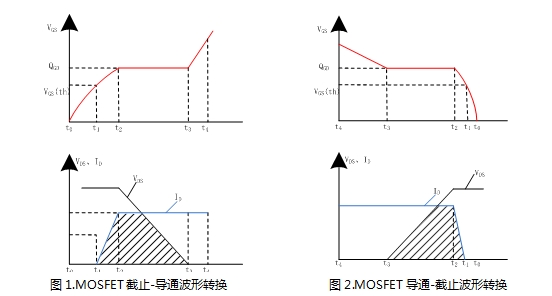

MOSFET的损耗主要有以下部分组成:1.通态损耗;2.导通损耗;3.关断损耗;4.驱动

关键字:

MOSFET EMI

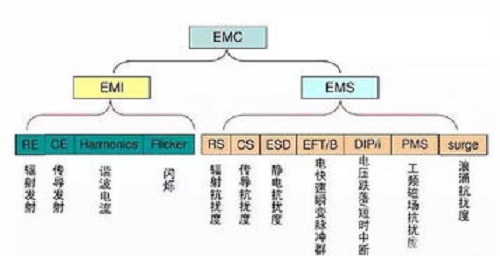

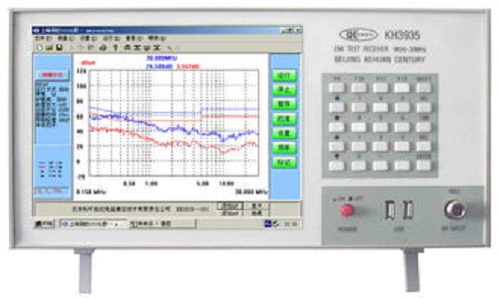

现在,受到EMC(电磁兼容性)问题困扰的技术人员越来越多。这是因为随着产品向多功能化、高功能化和高速化发展,EMC对策的难度也与日俱增。车载电子产品称得上是一个典型的代表。对此,日本Qualtec可靠性测试中心所长前野刚指出:“只要掌握了诀窍,就能找到EMC解决方法。”围绕EMC对策当前的课题和对策的重点,前野所长接受了记者采访。

——听说以车载电子产品为代表,对于最近的电子产品,很多电路设计人员都在为EMC对策犯愁。首先请您用外行也能理解的语言,

关键字:

EMC EMI

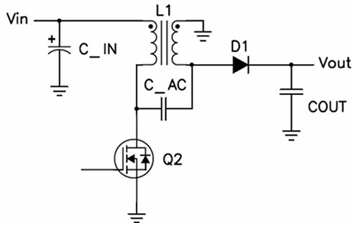

在不要求主级电路和次级电路之间电气隔离且输入电压高于或者低于输出电压时,SEPIC 是一种非常有用的拓扑。在要求短路电路保护时,我们可以使用它来代替升压转换器。SEPIC 转换器的特点是单开关工作和连续输入电流,从而带来较低的电磁干扰 (EMI)。这种拓扑(如图 1 所示)可使用两个单独的电感(或者由于电感的电压波形类似),因此还可以使用一个耦合电感,如图所示。因其体积和成本均小于两个单独的电感,耦合电感颇具吸引力。其存在的缺点是标准电感并非总是针对全部可能的应用进行优化。

关键字:

SEPIC EMI

随着电子产品迅速走向随身使用化、功能强大化与低功耗化,半导体技术的持续微缩就没有停止的可能性。然而,这样的演变趋势造就了电子产品‘使用可靠性的设计工作’重要性和电子产品‘功能的设计工作’本身一样重要。

这是因为外在的暂态杂讯干扰能量变得很容易进入电子产品内部,加上电子产品内部的晶片零组件因半导体微缩而变得十分孱弱,从而导致电子产品本身的正常运作就变得易于受到干扰与破坏。

Silicon Labs执行长Tyson T

关键字:

ESD EOS

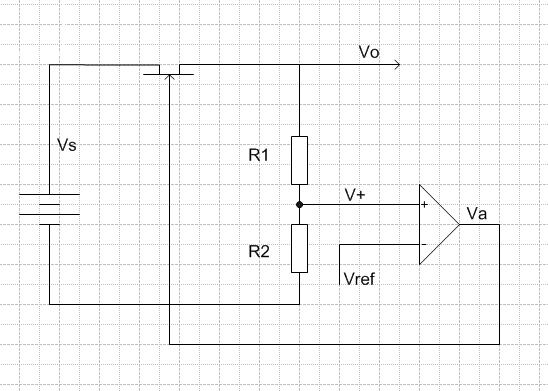

电容感测在很多应用中大展拳脚,从接近度检测和手势识别,到液面感测。无论是哪种应用,电容感测的决定性因素都是根据一个特定的基准来感测传感器电容值变化的能力。根据特定应用和系统要求的不同,你也许需要不同的方法来测量这个变化。在这篇博文章,我将介绍2个特定的架构类型—开关电容器电路和电感器-电容器LC谐振槽路—这是当前一种用于电容感测的电路。 开关电容器电路 图1显示的是针对电容感测的经简化电路,它以电荷转移为基础;电路中的开关执行采样保持运行。在采样之间,传感器电感器上的电荷的变化会导致输出电压的变化

关键字:

电容 EMI

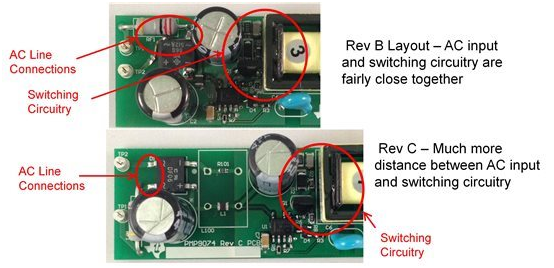

这里,我们先着重讨论当寄生电容直接耦合到电源输入电线时会发生的情况。 1.只需几fF的杂散电容就会导致EMI扫描失败。从本质上讲,开关电源具有提供高 dV/dt 的节点。寄生电容与高 dV/dt 的混合会产生 EMI 问题。在寄生电容的另一端连接至电源输入端时,会有少量电流直接泵送至电源线。 2.查看电源中的寄生电容。我们都记得物理课上讲过,两个导体之间的电容与导体表面积成正比,与二者之间的距离成反比。查看电路中的每个节点,并特别注意具有高 dV/dt 的节点。想想电路布局中该节点的表面积是多少,

关键字:

EMI

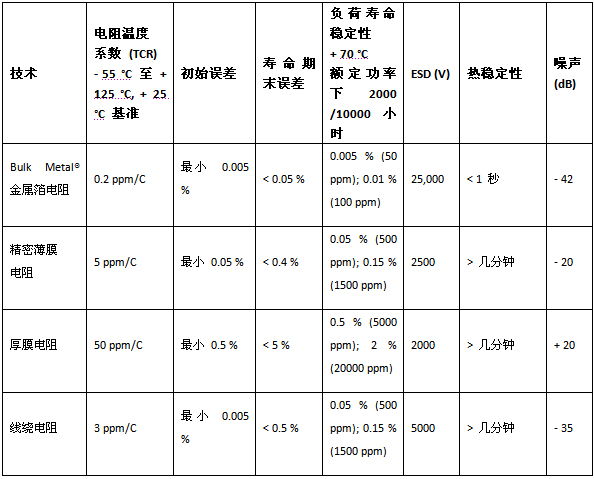

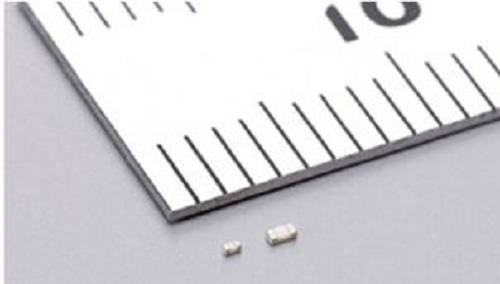

近二十年来,电子工业以惊人的速度发展。新技术的进步在减小设备尺寸的同时,也加大了分立元件制造商开发理想性能器件的压力。 在这些器件中,晶片电阻当前始终保持很高的需求,并且是许多电路的基础构件。它们的空间利用率优于分立式封装电阻,减少了组装前期准备的工作量。随着应用的普及,晶片电阻具有越来越重要的作用。主要参数包括 ESD 保护、热电动势 (EMF)、电阻热系数 (TCR)、自热性、长期稳定性、功率系数和噪声等。 以下技术对比中将讨论线绕电阻在精密电路中的应用

关键字:

电阻 ESD

让我们从几个示例开始。在这些示例中,我们试着保护系统不受以下情况的影响:

在静电放电 (ESD) 不安全的环境中安装或校准某些系统,这样做会导致ESD损坏。 工业控制系统往往跨越很远距离并且有可能暴露在自然危险下,诸如雷击,的大型系统。 与环境寄生效应耦合在一起的开关瞬变会生成高频辐射和耦合射线。

你在保护模拟输出时所需要应对的瞬变情况与其生成的低压 (<24V) 和低频 (<10kHz) 信号十分不同。工业瞬变是高电压

关键字:

TIPD153 ESD

ESD试验作为EMC测试标准的一项基本测试项目,如果产品的前期设计考虑不足,加上经验不够的话,往往会让人焦头烂额。一般中小型企业,如果没有专门的EMC工程师,往往这项工作就必须由硬件工程师来承担。对于整机来说,ESD抗扰能力不仅仅来自芯片的ESD耐压,PCB的布局布线,甚至与工艺结构也有密切关系。

常见的ESD试验等级为接触放电:1级——2KV;2级——4KV;3级——6KV;4级—&

关键字:

EMC ESD

献给那些刚开始或即将开始设计硬件电路的人。时光飞逝,离俺最初画第一块电路已有3年。刚刚开始接触电路板的时候,与你一样,俺充满了疑惑同时又带着些兴奋。在网上许多关于硬件电路的经验、知识让人目不暇接。像信号完整性,EMI,PS设计准会把你搞晕。别急,一切要慢慢来。

1)总体思路。设计硬件电路,大的框架和架构要搞清楚,但要做到这一点还真不容易。有些大框架也许自己的老板、老师已经想好,自己只是把思路具体实现;但也有些要自己设计框架的,那就要搞清楚要实现什么功能,然后找找有否能实现同样或相似功能的参考电路

关键字:

EMI BOM

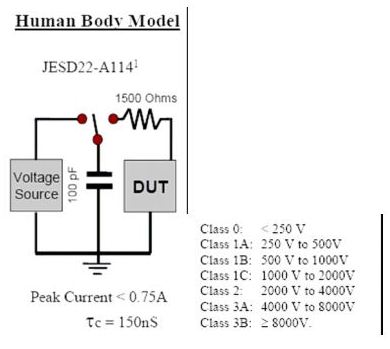

ESD:Electrostatic Discharge,即是静电放电,每个从事硬件设计和生产的工程师都必须掌握 ESD 的相关知识。为了定量表征 ESD 特性,一般将 ESD 转化成模型表达方式,ESD 的模型有很多种,下面介绍最常用的三种。

1.HBM:Human Body Model,人体模型:

该模型表征人体带电接触器件放电,Rb 为等效人体电阻,Cb 为等效人体电容。等效电路如下图。图中同时给出了器件 HBM 模型的 ESD 等级。

ESD人体模型

关键字:

ESD 静电放电

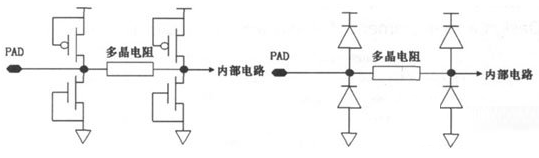

简介:大部分的ESD电流来自电路外部,因此ESD保护电路一般设计在PAD旁,I/O电路内部。典型的I/O电路由输出驱动和输入接收器两部分组成。ESD 通过PAD导入芯片内部,因此I/O里所有与PAD直接相连的器件都需要建立与之平行的ESD低阻旁路,将ESD电流引入电压线,再由电压线分布到芯片各个管脚,降低ESD的影响。

引言

静电放电会给电子器件带来破坏性的后果,它是造成集成电路失效的主要原因之一。随着集成电路工艺不断发展,CMOS电路的特征尺寸不断缩小,管子的栅氧 厚度越来越薄,芯片的面

关键字:

CMOS ESD

摘要: 本文主要阐述了MOSFET在模块电源中的应用,分析了MOSFET损耗特点,提出了优化方法;并且阐述了优化方法与EMI之间的关系。

关键词:MOSFET 损耗分析 EMI 金升阳R3

一、引言

MOSFET作为主要的开关功率器件之一,被大量应用于模块电源。了解MOSFET的损耗组成并对其分析,有利于优化MOSFET损耗,提高模块电源的功率;但是一味的减少MOSFET的损耗及其他方面的损耗,反而会引起更严重的EMI问题,导致整个系统不能稳定工作。所以需要在减少MOSFET的损耗

关键字:

MOSFET EMI

简介:本人是做手机硬件的,实际上是打杂的。日常的工作都是一些比较琐碎杂乱的事情,比如焊接、测试、校准、维修、打静电等等。工作差不多两年了,虽然经验丰富不多,但在不断地重复工作中也有些自己的总结,希望与大家分享一下。因为我们做的是国内的客户,客户入网的比较多。所以对静电的要求比较高。而不入网的客户的机子的外壳也大多是锌合金的,ESD问题也让人头痛。这里主要是想分享一下自己对静电方面的一些经验。

在必要的IO口加上TVS管如TP线、侧键的IO线、开关键。不推荐用压敏电阻。因为现在的压敏电阻太水了,根

关键字:

ESD Vbat

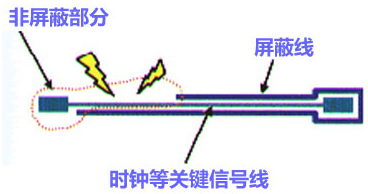

随着信号上升沿时间的减小及信号频率的提高,电子产品的EMI问题越来越受到电子工程师的关注,几乎60%的EMI问题都可以通过高速PCB来解决。以下是九大规则:

规则一:高速信号走线屏蔽规则

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

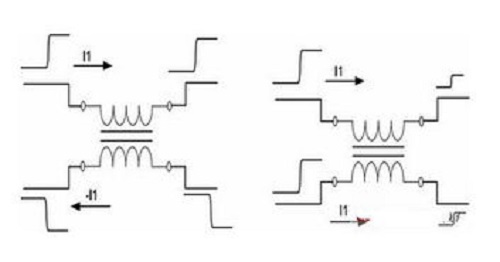

规则二:高速信号的走线闭环规则

由于PCB板的密度越来越高,很多PCB LAY

关键字:

PCB EMI

emi+esd介绍

您好,目前还没有人创建词条emi+esd!

欢迎您创建该词条,阐述对emi+esd的理解,并与今后在此搜索emi+esd的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473