- 是德科技公司日前宣布与 YellowSys 携手推出 U5303A 12 位 PCle® 高速数据采集卡,该产品提供专为光学相干断层成像(OCT)技术设计的新选件。YellowSys 是一家 IP 处理固件和软件供应商。

是德科技数据采集解决方案使用信号重采样方法,为极差分析提供板上增强,并提供稳定的 ADC 信号采样节奏。该解决方案主要关注信号采集过程中的时钟稳定性,以避免采样节奏发生变化。在使用外部 k 时钟时,通常会对信号采集产生不利影响。此外,信号处理直接在数据采集卡上实时进行,

- 关键字:

是德科技 U5303A FPGA

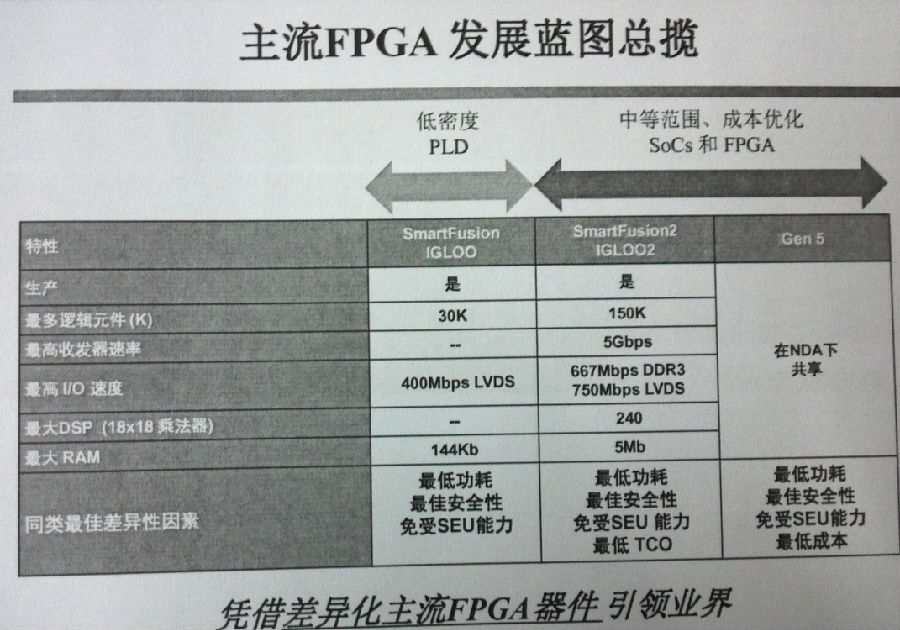

- 新年伊始,美高森美(Microsemi)全球市场营销执行副总裁Russ Garcia向媒体展示了一个全新的美高森美。 全新体现在:美高森美的营收在过去五年里增长了一倍。2014财年,营收为11.4亿美元。焦点市场集中在通信(占总营收的38%)、国防和安全(28%)、航空航天(13%)以及工业(23%)。几年来,通过不断地并购和通过创新实现自有产品的内生增长,美高森美不断成长为产品线多样,多元化发展的公司。 Russ Garcia透露,2015的美高森美将在以下三个领域更上层楼:

- 关键字:

美高森美 FPGA 分立器件 原子钟

- 长期以来很多新入群的菜鸟们总 是在重复的问一些非常简单但是又让新手困惑不解的问题。作为管理员经常要给这些菜鸟们普及基础知识,但是非常不幸的是很多菜鸟怀着一种浮躁的心态来学习 FPGA,总是急于求成。

再加上国内大量有关FPGA的垃圾教材的误导,所以很多菜鸟始终无法入门。为什么大量的人会觉得FPGA难学?作为著名FPGA 提供商Altera授权的金牌培训师,本管理员决心开贴来详细讲一下菜鸟觉得FPGA难学的几大原因。

1、不熟悉 FPGA的内部结构,不了解可编程逻辑器件的基本原理。

F

- 关键字:

Altera FPGA SRAM

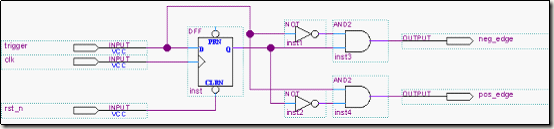

- 一、为什么要讲边沿检测

也许,没有那么一本教科书,会说到这个重要的思想;也许,学了很久的你,有可能不知道这个重要的思想吧。很惭愧,我也是在当年学了1年后才领悟到这个思想的。

说实话,我的成长很艰辛,没有人能给我系统的指导,而我得撑起这一片蓝天,于是乎无数个漏洞,我一直在修补我的不足。我没能对自己满足过,不是说我“贪得无厌”,而是,我不够“完美”。人可以不完美,但不可以不追求完美;或许终点永远达不到,但努力的过程,你一直在靠近完美;有方向感地奋

- 关键字:

FPGA 边沿检测

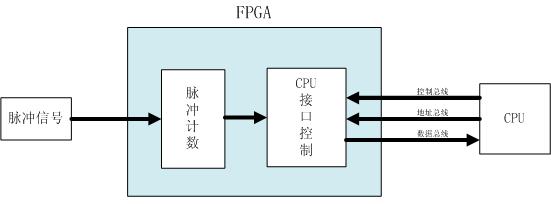

- 上次提出了一个处于异步时钟域的MCU与FPGA直接通信的实现方式,其实在这之前,特权同学想列举一个异步时钟域中出现的很典型的问题。也就是要用一个反例来说明没有足够重视异步通信会给整个设计带来什么样的危害。

特权同学要举的这个反例是真真切切的在某个项目上发生过的,很具有代表性。它不仅会涉及使用组合逻辑和时序逻辑在异步通信中的优劣、而且能把亚稳态的危害活生生的展现在你面前。

从这个模块要实现的功能说起吧,如图1所示,实现的功能其实很简单的,就是一个频率计,只不过FPGA除了脉冲采集进行计数外,

- 关键字:

FPGA 同步设计

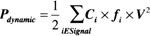

- 从Xilinx公司推出FPGA二十多年来,研发工作大大提高了FPGA的速度和面积效率,缩小了FPGA与ASIC之间的差距,使FPGA成为实现数字电路的优选平台。今天,功耗日益成为FPGA供应商及其客户关注的问题。

降低FPGA功耗是降低封装和散热成本、提高器件可靠性以及打开移动电子设备等新兴市场之门的关键。

Xilinx在提供低功耗FPGA解决方案方面较有经验。本文说明如何应用计算机辅助设计(CAD)技术,如Xilinx ISE(集成软件环境)9.2i版本软件使功能有效降低。

CMO

- 关键字:

FPGA ISE

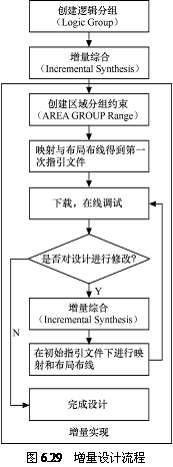

- 6.9 典型实例12:增量式设计(Incremental Design)演示

6.9.1 实例的内容及目标

1.实例的主要内容

6.7节对增量式设计这一方法的基本概念和流程做了全面的介绍。本节将以一个具体的实例帮助读者熟悉增量式设计的操作流程。

本实例的源代码参见随书光盘Example6.9。此程序为PC机通过串口向SRAM写入数据,再由FPGA从SRAM中读取数据通过串口将其送到PC机。

本实例的重点在于设计过程中是如何应用增量式设计的,而不是如何实现程序本身的功能。

- 关键字:

FPGA ISE

- 6.8 典型实例11:ChipScope功能演示

6.8.1 实例的内容及目标

1.实例的主要内容

本节通过一个简单的计数器,使用ChipScope的两种实现流程,基于Xilinx开发板完成设计至验证的完整过程。本实例的工作环境如下。

· 设计软件:ISE 7.1i。

· 综合工具:ISE自带的XST。

· 仿真软件:ModelSim SE 5.8C。

· 在线调试:ChipScope Pro 8.2i。

- 关键字:

FPGA ISE

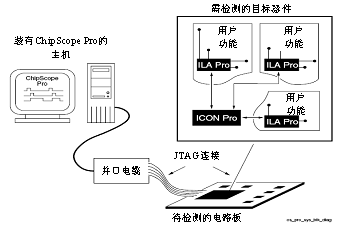

- 6.7 片上逻辑分析仪(ChipScope Pro)使用技巧

在FPGA的调试阶段,传统的方法在设计FPGA的PCB板时,保留一定数量的FPGA管脚作为测试管脚。在调试的时候将要测试的信号引到测试管脚,用逻辑分析仪观察内部信号。

这种方法存在很多弊端:一是逻辑分析仪价格高昂,每个公司拥有的数量有限,在研发期间往往供不应求,影响进度;二是PCB布线后测试脚的数量就确定了,不能灵活地增加,当测试脚不够用时会影响测试,测试管脚太多又影响PCB布局布线。

ChipScope Pro是ISE下

- 关键字:

FPGA ISE

- 6.6 增量式设计(Incremental Design)技巧

本节将对ISE下增量式设计做一个全面的介绍。FPGA作为一种现场可编程逻辑器件,其现场可重编程特性能够提高调试速度。每次硬件工程师可以很方便地改变设计,重新进行综合、实现、布局布线,并对整个设计重新编程。

然而当设计算法比较复杂时,每一次综合、实现、布局布线需要花很长的时间。即使仅仅改变设计中的一点,也会使综合编译的时间成倍增加。而且更为麻烦的是如果整个工程的运行频率很高,对时序的要求也很严格,这样重新布线往往会造成整个时序错

- 关键字:

FPGA ISE

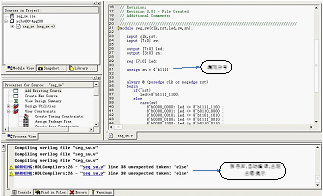

- 6.5 编译与仿真设计工程

编写代码完成之后,一个很重要的工作就是验证代码功能的正确性,这就需要对代码进行编译与仿真。编译主要是为了检查代码是否存在语法错误,仿真主要为了验证代码实现的功能是否正确。

编译和仿真设计工程在整个设计中占有很重要的地位。因为代码功能不正确或代码的编写风格不好对后期的设计会有很大的影响,所以需要花很多时间在设计工程的仿真上。

在这一节中将通过一个具体的实例来介绍如何对编译工程代码以及如何使用ISE自带的仿真工具ISE Simulator进行仿真。

1.

- 关键字:

FPGA ISE

- 6.4 创建设计工程

本节将重点讲述如何在ISE下创建一个新的工程。要完成一个设计,第一步要做的就是新建一个工程。具体创建一个工程有以下几个步骤。

(1)打开Project Navigator,启动ISE集成环境。

ISE的启动请参见6.2节。

(2)选择“File”/“New Project”菜单项,启动新建工程对话框。

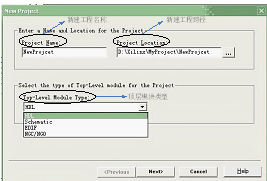

会弹出如图6.9的对话框。

如图6.9所示,新建工程时需要设置工程名称和新建工程的路径,还要设置

- 关键字:

FPGA ISE

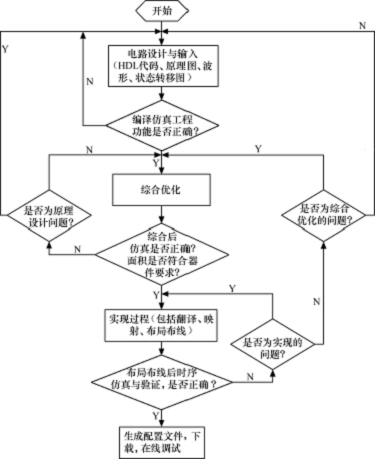

- 6.3 ISE软件的设计流程

Xilinx公司的ISE软件是一套用以开发Xilinx公司的FPGA&CPLD的集成开发软件,它提供给用户一个从设计输入到综合、布线、仿真、下载的全套解决方案,并很方便地同其他EDA工具接口。

其中,原理图输入用的是第三方软件ECS;状态图输入用的是StateCAD;HDL综合可以使用Xilinx公司开发的XST、Synopsys公司开发的FPGA Express和Synplicity公司的Synplify/Synplify Pro等;测试激励可以是图

- 关键字:

FPGA Xilinx ISE

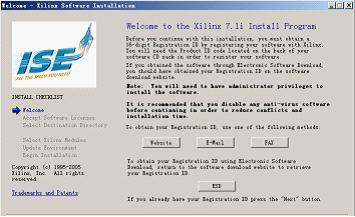

- 6.2 ISE软件的安装与启动

6.2.1 ISE软件的安装

ISE的安装改变了license管理方式,在安装后并不需要任何license支持,仅仅是在这安装过程式中输入ISE的注册序列号(Register ID)即可。ISE 7.1i安装启动界面如图6.1所示。

图6.1 ISE 7.1i安装启动界面

安装ISE时只需要根据所选的版本是在PC机或工作站上,然后根据软件的提示安装即可,这里不做详细叙述,只对安装的几个问题进行说明。

1.环境变量

- 关键字:

FPGA ISE

- ISE软件简介

Xilinx作为当界上最大的FPGA/CPLD生产商之一,长期以来一直推动着FPGA/CPLD技术的发展。其开发的软件也不断升级换代,由早期的Foundation系列逐步发展到目前的ISE 9.x系列。

ISE是集成综合环境的缩写,它是Xillinx FPGA/CPLD的综合性集成设计平台,该平台集成了设计、输入、仿真、逻辑综合、布局布线与实现、时序分板、芯片下载与配置、功率分析等几乎所有设计流程所需工具。

ISE系列软件分为4个系列:WebPACK、BaseX、Fo

- 关键字:

FPGA ISE

dsp+fpga介绍

您好,目前还没有人创建词条dsp+fpga!

欢迎您创建该词条,阐述对dsp+fpga的理解,并与今后在此搜索dsp+fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473