市场研究机构ICInsights最新报告称,中国IC设计企业在2014年全球前五十无晶圆厂IC供应商排行榜上占据9个席位。这9家厂商包括海思、展讯、大唐微、南瑞智芯、华大、中兴、瑞芯微、锐迪科、全志。而2009年只有1家企业入围,这表明中国无晶圆厂IC产业确实成长显著。

然而,上述9家入围企业中,有5家都聚焦于目前最热门的智能手机市场。当然,这些年智能手机终端产业确实增长迅速,也为中国IC设计提供了发展空间和机遇。但我国拥有的是全球最大的信息消费市场,每年进口集成电路产品超过2000亿美元,对I

关键字:

海思 展讯 FPGA

对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可控。

下文总结了几种进行时序约束的方法。按照从易到难的顺序排列如下:

0.核心频率约束

这是最基本的,所以标号为0.

1.核心频率约束+时序例外约束

时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay.但这还不是最完整的时序约束

关键字:

FPGA 时序约束

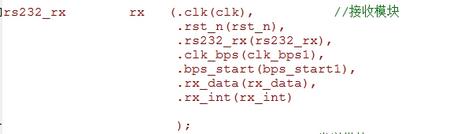

以前在学单片机的时候,觉得串口通信其实很简单,只要一个指令数据就能轻易的接收或者发送。前几天试着用FPGA实现,发现里面的学问还不少,并没有想象的那么简单。当然代码肯定是参考别人的,不过我还是认真研究了整段代码的,下面的程序就是我在看懂了别人代码后自己敲的,花了也不少时间,理解的也差不多,下面我就在这里给那些和我一样的初学者介绍一下吧,解释的不对的地方还望各位大神指正,大家好一起学习~

1、顶层模块

写程序都一样,不能多有的程序都写在一个模块里,那样看起来很麻烦,出了错误也不好维护,对于一

关键字:

FPGA 状态机

一、关于HDL

1. HDL简介

HDL : Hardware Discription Language 硬件描述语言,即描述FPGA/CPLD内部逻辑门的工作状态,来实现一定电路。

随着EDA技术的发展,使用硬件语言设计PLD/FPGA成为一种趋势。目前硬件描述语言有VHDL、Verilog、Superlog、System C、Cynlib C++、C Level等。 各种语言有各种优势,根据业界应用而定。

2. VHDL和Verilog区别

在业界,VHDL和Veri

关键字:

FPGA Verilog

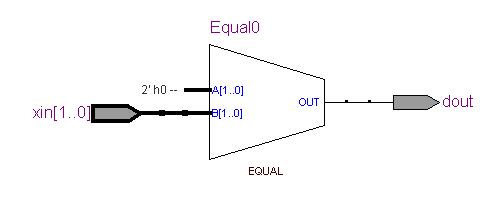

刚开始玩CPLD/FPGA开发板的时候使用的一块基于EPM240T100的板子,alter的这块芯片虽说功耗小体积小,但是资源还是很小的,你写点稍微复杂的程序,如果不注意coding style,很容易就溢出了。当时做一个三位数的解码基本就让我苦死了,对coding style的重要性也算是有一个比较深刻的认识了。

后来因为一直在玩xilinx的spartan3 xc3s400,这块芯片资源相当丰富,甚至于我在它里面缓存了一帧640*480*3/8BYTE的数据都没有问题(VGA显示用)。而最近

关键字:

FPGA verilog RTL

学习FPGA其实也不算久,开始的时候参考别人的代码并不多,大多是自己写的,那时候做时序逻辑多一些。参加了中嵌的培训班,一个多月的时间在熟悉ISE软件的使用以及verilog语法方面下了苦功,也参考了不少书,算是为自己打下了比较好的基础。因为那时候培训的方向是软件无线电方面的,所以做了很多有关的模块程序,之前的日志里也发表了很多,关键是一个兴趣,感觉仿真后看到自己的一个个算法思想得到实现真有成就感。后来停了一段时间,因为实在没有比较有意思的活干了。

直到前段时间开始使用SP306的开发板,然后会参

关键字:

FPGA verilog

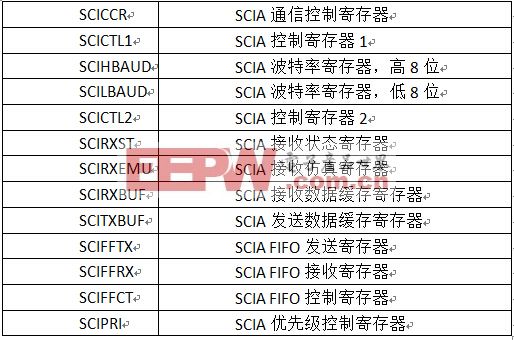

一、概述

SCI(serial communication interface)即串行通信接口,是一个双线异步串行口,一般用作UART。TMS320F2802X的内部具有一个SCIA模块,每个SCI模块都各有一个接收器和发送器。SCI的接收器和发送器各有一个4级深度的FIFO(first in first out 先入先出)队列,它们都有自己独立的使能位和中断位,可以在半双工通信中进行独立操作,或者在全双工通信中进行操作。TMS320F2802X的SCI模块具有以下特点:

1. 和普通I/

关键字:

Proteus DSP SCI

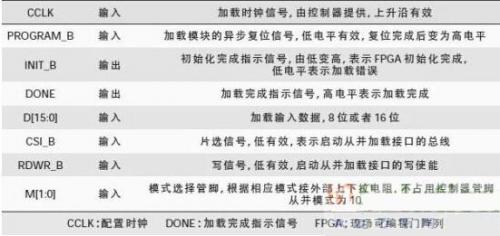

现场可编程门阵列(FPGA)作为专用集成电路(ASIC)领域的一种半定制电路,可以根据设计的需要灵活实现各种接口或者总线的输出,在设备端的通信产品中已得到越来越广泛的使用。FPGA是基于静态随机存储器(SRAM)结构的,断电后程序丢失后的每次上电都需要重新加载程序。且随着FPGA规模的升级,加载程序的容量也越来越大,如Xilinx公司的Spartan - 6系列中的6SLX150T,其加载容量最大可以达到4.125 MB.

1 FPGA常用配置方式

FPGA的配置数据通常存放在系统中的存储

关键字:

CPLD FPGA modelsim

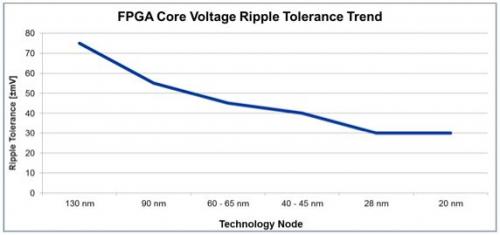

如果设计师可以在开发过程早期就满足基于FPGA的设计,提出的功耗要求和约束条件,那么在系统的最终实现阶段就能形成极具竞争力的优势。然而,根据整个技术文献中这种自我暗示式的反复祷告,今天基于FPGA的系统中还有什么会使得完全遵循这个建议变得不切实际或过于困难呢?尽管能够使用各种开发工具,如专门针对FPGA项目开发的早期功耗预估器和功耗分析器,但对电源设计师来说,在设计过程早期就考虑最坏情况而不是最佳情况的电源系统是有好处的,因为在许多方面仍有太多的不确定性,比如在硬件设计完成和功耗可以测量之前,静态小电

关键字:

FPGA 电源设计

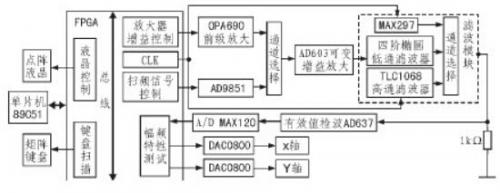

以单片机和可编程逻辑器件(FPGA)为控制核心,设计了一个程控滤波器,实现了小信号程控放大、程控调整滤波器截止频率和幅频特性测试的功能。其中放大模块由可变增益放大器AD603实现,最大增益60dB,10dB步进可调,增益误差小于1%.程控滤波模块由MAX297低通滤波、TLC1068高通滤波及椭圆低通滤波器构成,滤波模式用模拟开关选择。本系统程控调整有源滤波的-3dB截止频率,使其在1~30kHz范围内可调,误差小于1.5%.此外,采用有效值采样芯片AD637及12位并行A/D转换器MAX120实现了

关键字:

单片机 FPGA AD637

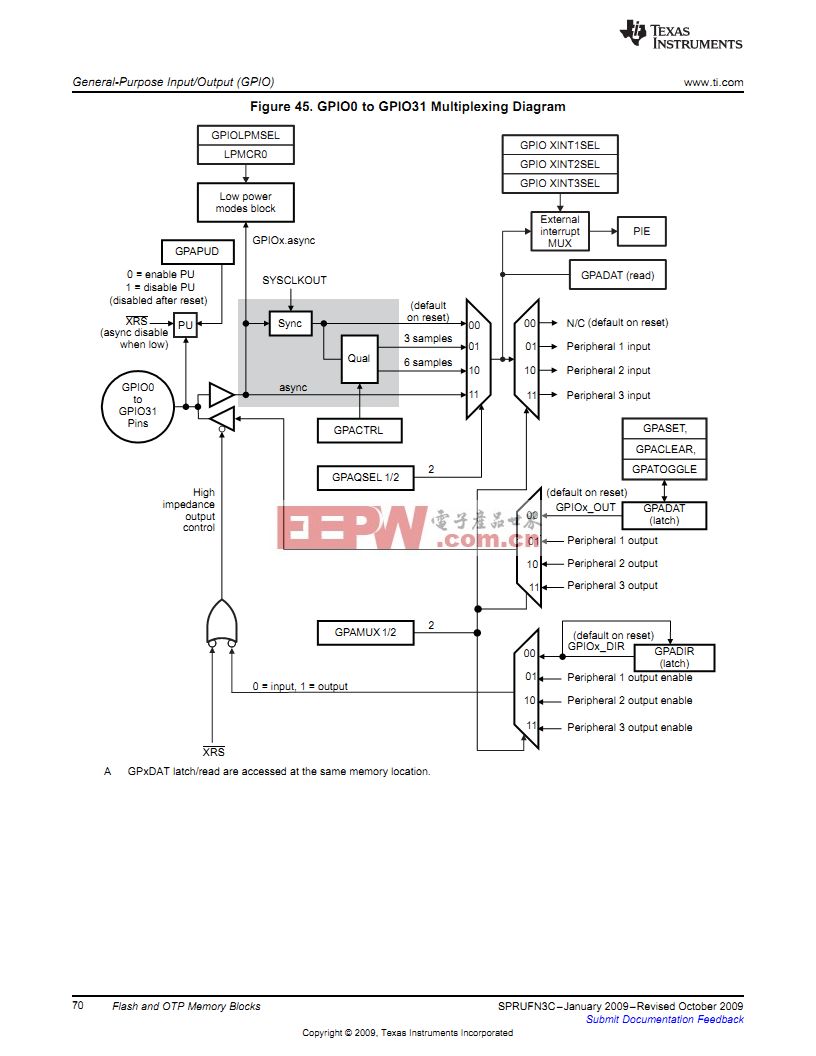

一、TMS320F2802X的GPIO概述

TMS320F2802X的每个GPIO引脚除了具有GPIO功能外,还可复用最多三种独立的外设功能。每个器件共有3个端口,端口A包括GPIO0-GPIO31,端口B包括GPIO32-GPIO38,模块端口包括AIO0-AIO15.

下图为TMS320F2802X典型GPIO端口A内部结构图。

二、TMS320F2802X的GPIO寄存器

引脚功能分配、输入限制条件,外部中断源都是通过GPIO配置寄存器来控制。另外,你可以分配引脚将设

关键字:

Proteus DSP

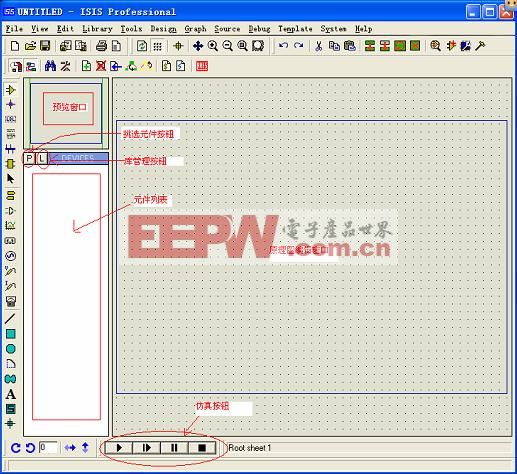

Proteus软件是英国Lab Center Electronics公司出版的EDA工具软件公司的一款电路设计与仿真软件,它包括ISIS,ARES等软件模块,其中ARES模块主要用来完成PCB设计,而ISIS模块主要用来完成电路原理图的设计与仿真。Proteus的软件仿真基于VSM技术,与其他仿真软件的不同也是最大的优势在于它能够仿真大量的单片机芯片,主要包括MCS-51系列,PIC系列,AVR系列,ARM系列等等,软件配备了大最的单片机外围电路与单片机配合,如键盘、LED、LCD、ADC、DAC、存

关键字:

Proteus DSP

AMD宣布其嵌入式 Radeon HD 7850 GPU 协助Analogic公司旗下 BK Ultrasound 医用超音波产品的超音波系统 bk3000 发挥卓越应用效能。新款 BK Ultrasound 医用超音波 bk3000 搭载AMD嵌入式 Radeon 绘图技术,可望使成像及系统效能到全新境界。

AMD嵌入式 Radeon HD 7850 GPU 采用AMD屡屡获奖的次世代绘图核心(GCN)架构为基础,带动各种嵌入式应用在视觉与平行处理功能提升。除了超音波外, GPGPU 的其他应

关键字:

AMD嵌 Radeon GPU FPGA

致力于在电源、安全、可靠和性能方面提供差异化半导体技术方案的领先供应商美高森美公司(Microsemi Corporation) 宣布完成9项全新的美国国家标准与技术研究所(National Institute of Standards and Technology, NIST)加密算法验证程序(CAVP)认证。

美高森美SmartFusion®2 SoC FPGA和 IGLOO®2 FPGA通过的认证项目包括NIST “Suite B”中的AES加密/解

关键字:

美高森美 NIST FPGA

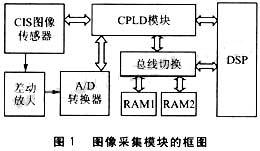

接触式图像传感器CIS( CONTACT Image SENSOR )是继CCD之后于20世纪90年代研究和开发的一种新型光电耦合器件[1]。它将光电传感阵列、LED光源阵列、柱状透镜阵列、移位寄存器和模拟开关等集成在一个条状方形盒内,其工作原理与CCD较为相似,但与CCD相比,CIS具有体积小、价格低、结构简单、安装方便等优点,目前在传真机、扫描仪及条码*器等领域可完全取代CCD图像传感器。

本文介绍一种基于复杂可编程逻辑器件CPLD(Complex Programmable LOGIC DE

关键字:

CPLD DSP 图像传感器

dsp+fpga介绍

您好,目前还没有人创建词条dsp+fpga!

欢迎您创建该词条,阐述对dsp+fpga的理解,并与今后在此搜索dsp+fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473