- 015年 3月 17日至 19 日,京微雅格(北京)科技有限公司参加了在上海举行的 2015慕尼黑上海电子展。活动期间,京微雅格将展示其FPGA产品在多个市场领域的应用方案,包括消费电子、智能家居、金融安全、机器人、物联网、汽车电子等。

FPGA芯片被称为“万能芯片”,它和专业集成电路的区别就在于:从技术角度来说,它是一种可以编程的产品,在不改变芯片本身硬件组成的情况下可以反复使用。根据市场变化,在同样的载体上实现不同功能,而且不用更改硬件载体。听起来很美好,但研发起来很

- 关键字:

京微雅格 FPGA

- Altera公司在OFC 2015上为光传送网展示了两款产品,采用了Arria® 10 FPGA设计实现:Altera SoftSilicon® 400G转发器/复用转发器(TPO516)和Altera SoftSilicon单芯片20通道任意速率映射器 (TPOC226),支持分段和重组(SAR)功能。系统规划人员设计高级ODU交叉连接系统来处理基于OTN的传送功能时,该产品帮助他们降低了复杂度。基于Altera的20 nm Arria 10 FPGA——并提

- 关键字:

Altera FPGA

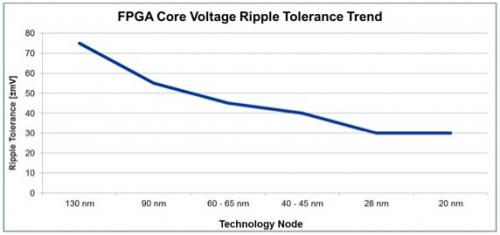

- 在开发过程一开始时,如果设计人员就能够满足基于FPGA的设计对电源的要求和约束,这对于系统的最终实现而言是很大的竞争优势。但是,虽然技术文献在这方面进行了大量的介绍,目前基于FPGA的系统中是否有不实用或者很难实现的东西导致做不到这一点?尽管可以使用各种开发工具,例如特别针对FPGA工程的早期功耗估算器和功耗分析器等,电源设计人员最好能够在设计早期阶段,考虑电源系统的最差情况,而不是最佳情况,这是因为在硬件设计完成之后,测量功耗之前,动态负载需求还有很大的不确定性,会在静态低电流状态和全速工作状态之间

- 关键字:

FPGA 电源系统

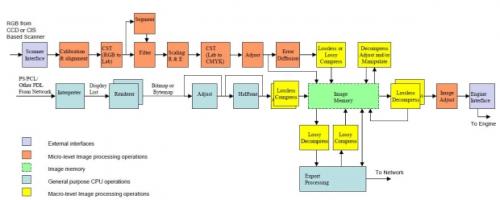

- 在高性能计算、娱乐和科学计算市场,OpenCL的采用在持续增长。OpenCL的灵活性和便携性使之成为了一个开发图像处理应用的优秀平台。然而,OpenCL尚未应用到硬拷贝打印机和多功能打印机(MFP)市场。传统上,打印机/MFP市场使用全定制系统级芯片(SoC或ASIC)、专用集成电路进行图像处理。在本文中,我们探讨了配合Altera SoC FPGA(现场可编程门阵列)的OpenCL在核心MFP图像处理流水线中的应用。核心图像处理流水线以每分钟大于90页信纸大小的全色RGB持续速率运行,图像分辨率为6

- 关键字:

FPGA OpenCL

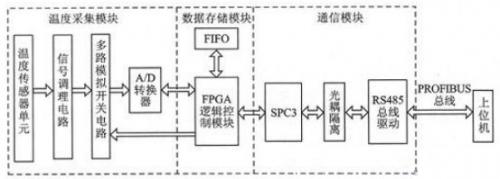

- 温度是表征物体冷热程度的物理量,是工业生产中常见和最基本的参数之一,在生产过程中常常需要对温度进行监控。传统的温度采集系统,通常采用单片机或数字信号处理器DSP作为微控制器,控制模数转换器ADC及其他外围设备的工作;但是,基于单片机或DSP的高速多路温度采集系统都有一定的不足。由于单片机运行的时钟频率较低,并且单片机是基于顺序语言的,各种功能都要靠软件的运行来实现,因此随着程序量的增加,如果程序的健壮性不好,会出现“程序跑飞”和“复位”现象。DSP的运算

- 关键字:

DSP SOPC

- 一、 引言

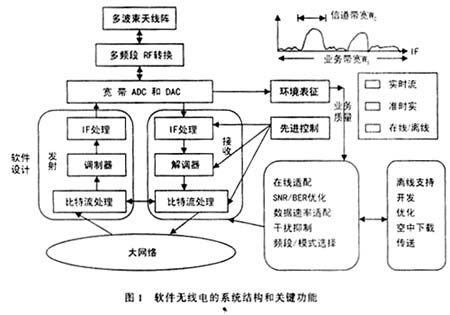

现代通信技术、微电子技术和计算机技术的飞速发展,促进了无线通信技术从数字化走向软件化。软件无线电的出现掀起了无线通信技术的又一次革命,它已经成为目前通信领域中最为重要的研究方向之一。所谓软件无线电,是指构造一个通用的、可重复编程的硬件平台,使其工作频段、调制解调方式、业务种类、数据速率与格式、控制协议等都可以进行重构和控制,选用不同的软件模块就可以实现不同类型和功能的无线电台,其核心思想是在尽可能靠近天线的地方使用宽带A/D和D/A变换器,并尽可能地用软件来定义无线功能[1]。

- 关键字:

FPGA 无线电

- 1 概述

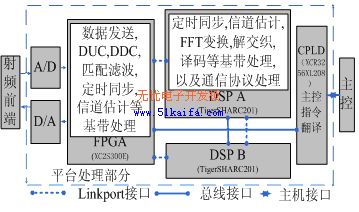

随着微电子技术的快速发展,可编程芯片的处理能力也在不断加强,尤其是DSP芯片正在朝着高速,多指令并行执行的方向发展。DSP处理能力的增强,使得原来运算量很大的算法可以用软件的方式快速实现。由于软件处理的灵活性,这给整体的无线电体系结构带来了深刻的变化。

软件无线电是指一种基于可编程的,具有一定灵活性的高速信号处理平台。处理平台上的设备都可以进行重新配置,将通用化、模块化、标准化的算法单元用软件方式实现,根据系统的实际需要,在软件中添加各种不同算法,可以完成特定的功能,因而可以跨越

- 关键字:

DSP 无线电

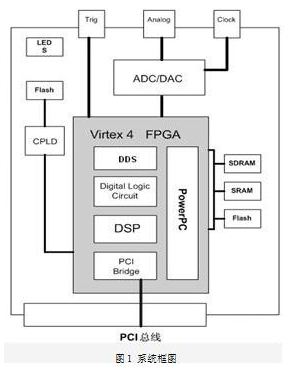

- 软件无线电的出现,是无线电通信从模拟到数字、从固定到移动后,由硬件到软件的第三次变革。简单地说,软件无线电就是一种基于通用硬件平台,并通 过软件可提供多种服务的、适应多种标准的、多频带多模式的、可重构可编程的无线电系统。软件无线电的关键思想是,将AD(DA)尽可能靠近天线和用软件来 完成尽可能多的无线电功能。

蜂窝移动通信系统已经发展到第三代,3G系统进入商业运行一方面需要解决不同标准的系统间的兼容性;另一方 面要求系统具有高度的灵活性和扩展升级能力,软件无线电技术无疑是最好的解决方案。用ASI

- 关键字:

无线电 FPGA

- 心率监控器是一款用于监测人体心跳速率的器件。心率的单位是bpm(每分钟心跳数)。人体的心跳速率根据其日常身体活动、睡眠和基本健康状况的不同而有所差别。本文为大家介绍几种心率计及心率监测系统的设计,供大家使用参考。

基于EFM32TG840的便携式心率计的设计方案

在消费电子领域,便携式电子产品由于体积小、质量轻的特点越来越受到消费者的喜爱,已成为人们生活中不可缺少的部分。基于这个思路,我们设计了一款便携式心率计,它可以替代用脉搏听诊器等进行测量的传统方法,使用非常方便。

一种便携式单

- 关键字:

FPGA VHDL

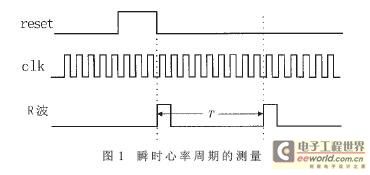

- 心率计是常用的医学检查设备,实时准确的心率测量在病人监控、临床治疗及体育竞赛等方面都有着广泛的应用。心率测量包括瞬时心率测量和平均心率测量。瞬时心率不仅能够反映心率的快慢。同时能反映心率是否匀齐;平均心率虽只能反映心率的快慢,但记录方便,因此这两个参数在测量时都是必要的。

测量心率有模拟和数字两种方法。模拟方法是在给定的时间间隔内计算R波(或脉搏波)的脉冲个数,然后将脉冲计数乘以一个适当的常数测量心率的。这种方法的缺点是测量误差较大、元件参数调试困难、可靠性差。数字方法是先测量相邻R波之间的时间

- 关键字:

FPGA 心率计

- 七、 测试平台设计

本实验主要对LED的输出和输入与复位的关系进行测试仿真,通过仿真,即可验证设计的正确性和合理性。相关testbench的代码如下:

以下是代码片段:

`timescale 1ns/1ns

module LED_Driver_tb;

reg Rst_n;

reg [3:0] Sig;

wire [3:0] Led;

LED_Driver

#( /*参数例化*/

.Width (4)

)

LED_Driver_in

- 关键字:

FPGA LED

- 在之前更新的目录里面,并没有安排这个实验,第一个实验应该是独立按键的检测与消抖。可是,当小梅哥来做按键消抖的实验时,才发现没有做基本的输出设备,因此按键检测的结果无法直观的展示出来。也算是为后续实验做铺垫吧,第一个实验就安排成了点亮LED灯。

一、 实验目的

实现4个LED灯的亮灭控制

二、 实验原理

LED灯的典型电路如下2-1所示,我们控制led灯的亮灭,实质就是去控制FPGA的IO输给LED负极一个低电平或者高电平。从图中可知,我们给对应的led负极上一个低电平,就会有对

- 关键字:

FPGA LED

- 2月底,Xilinx发布了下一代16nm产品特点的新闻:《Xilinx凭借新型存储器、3D-on-3D 和多处理SoC技术在16nm继续遥遥领先》(http://www.eepw.com.cn/article/270122.htm),大意是说,Xilinx新的16nm FPGA和SoC中,将会采用新型存储器UltraRAM, 3D晶体管(FinFET)和3D封装,Zynq会出多处理器产品MPSoC,因此继28nm和20nm之后,继续在行业中保持领先,打破了业内这样的规则:Xilinx和竞争对手在工艺上

- 关键字:

Xilinx FPGA

- 电能质量即电力系统中电能的质量。理想的电能应该是完美对称的正弦波。一些因素会使波形偏离对称正弦,由此便产生了电能质量问题。一方面我们研究存在哪些影响因素会导致电能质量问题,一方面我们研究这些因素会导致哪些方面的问题,最后,我们要研究如何消除这些因素,从而最大程度上使电能接近正弦波。本文为您介绍电能质量的检测与分析仪器设计汇总。

基于STM32和ATT7022C的电能质量监测终端的设计

本文以ARM STM32F103VE6和电表芯片ATT7022C为主构建了电能质量监测终端,利用电表芯片A

- 关键字:

ARM FPGA NiosⅡ

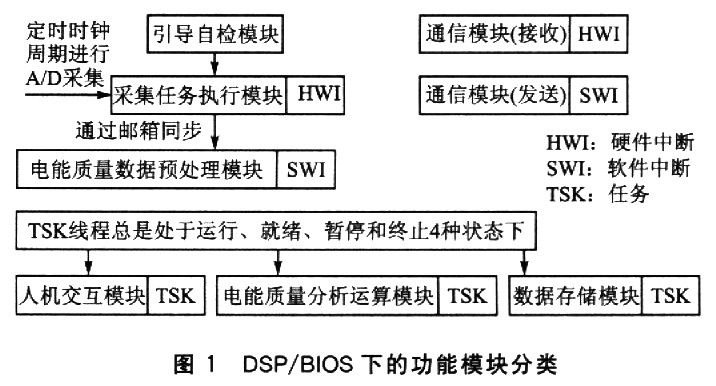

- DSP(数字信号处理器)在现今的工程应用中使用越来越频繁。其原因主要有三点:第一,它具有强大的运算能力,能够胜任FFT、数字滤波等各种数字信号处理算法;第二,各大DSP厂商都为自己的产品设计了相关的IDE(集成开发环境),使得DSP应用程序的开发如虎添翼;第三,具有高性价比,相对于它强大的性能,不高的价格有着绝对的竞争力。

TI为本公司的DSP设计了集成可视化开发环境CCS(Code Composer Studio),而DSP/BIOS是CCS的重要组成部分。它实质上是一种基于TMS320系列D

- 关键字:

DSP BIOS

dsp+fpga介绍

您好,目前还没有人创建词条dsp+fpga!

欢迎您创建该词条,阐述对dsp+fpga的理解,并与今后在此搜索dsp+fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473