1 引 言

具有梯形反电动势的永磁同步电动机通常被称为无刷直流电动机,它具有体积小、重量轻、效率高、惯量小和响应快等特点。无刷直流电动机采用电子换向器替代了传统直流电动机的机械换向装置,从而克服了电刷和换向器所引起的噪声、火花、电磁干扰、寿命短等一系列弊病。由于无刷直流电动机既具备交流电动机的结构简单、运行可靠、维护方便等一系列优点,又具有直流电动机的运行效率高、无励磁损耗以及调速性能好等诸多优点,故其在工业领域中的应用越来越广泛。

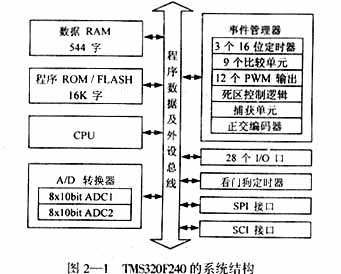

当前国内生产的电动执行器多由模拟器件控制,精度差;保护措

关键字:

DSP TMS320F240 BLDC

引言

对于机器人控制技术,实时性和稳定性是研究的重点。现阶段,机器人控制的主要方法是在离线状态下对步态进行规划,并在主控机上对机器人的运动进行实时的补偿,这种处理方法对处理器的运算速度和处理能力提出了很高的要求。传统的机器人控制器大多以80C196系列单片机作为处理器,当采用12MHz晶振时,其状态周期为167ns,机器周期为1ms,不能满足机器人控制的需要。

DSP芯片处理速度可以达到几纳秒,甚至更高,非常适合于机器人控制。因此,本文选用DSP来代替原有的单片机,同时借助底层电压反馈技术

关键字:

DSP 80C196

智能交通系统(ITS)的概念是美国智能交通学会于1990年提出的,它将先进的信息技术、通信技术、自动控制技术、电子技术及计算机处理技术综合运用于整个运输管理系统中,通过对交通信息的采集、传输和处理,对交通运输进行协调和管理,建立起实时、准确、高效的综合交通运输管理体系,从而提高了交通效率和安全了,实现性交通运输服务和管理的智能化。

智能车辆的导航与定位、自动驾驶与控制和车辆的预警防碰等智能交通系统关键技术的研究,近年来受到国内外越来越广泛的关注,也取得了丰硕的成果。但真正的实验研究还是很少,基本

关键字:

DSP 机器人

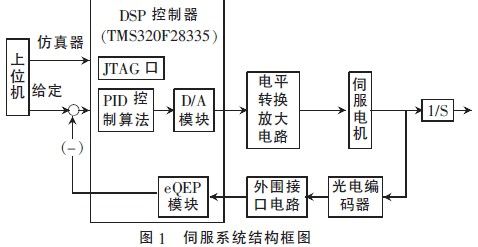

在伺服电机和伺服驱动器组成的高性能稳定平台伺服系统中,需要实时地获得伺服电机的转角和转速信息,高速高精度的传感器以及相应的外围电路设计是必不可少的。由于单片机自身资源的局限性,难以满足现在伺服系统高精度、高运算率以及快速实时性的要求。在稳定平台伺服控制系统中,DSP已经逐渐取代单片机,成为主流芯片。本设计采用TI公司的32 bit浮点型DSP芯片TMS320F28335,其工作时钟频率高达150 MHz,具有强大的运算能力,能够实时地完成复杂的控制算法。片内集成了丰富的电机控制外围部件和电路,简化了控

关键字:

DSP

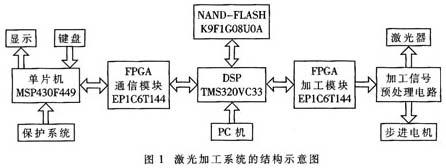

激光切割和雕刻以其精度高、视觉效果好等特性,被广泛运用于广告业和航模制造业。在大尺寸激光加工系统的开发过程中,加工速度与加工精度是首先要解决的问题。解决速度问题的一般方法是在电机每次运动前、后设置加、减速区,但这会使加工数据总量成倍增加。除此之外,庞大的数据计算量也需要一个专门的高性能处理器来实现。

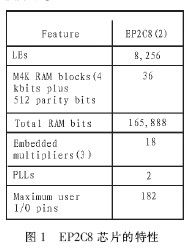

FPGA(现场可编程门阵列)在并行信号处理方面具有极大的优势。本系统采用FPGA作为加工数据的执行器件。这种解决方案突出的特点是让运动控制的处理部分以独立的、硬件性方式展开,增加系统的性能和可靠性,

关键字:

DSP FPGA

引言

长期以来,电动机作为机械能和电能的转换装置,在各个领域得到了广泛应用。无刷直流电动机综合了直流电动机和交流电动机的优点,既具有交流电动机结构简单、运行可靠、维护方便的特点,又具有直流电动机运行效率高、调速性能好的优点。正是这些优点使得无刷直流电动机在当今国民经济的很多领域得到了广泛的应用。无刷直流电动机采用电子换向装置,根据位置传感器检测到的位置信号,通过DSP(数字信号处理器)产生一定的逻辑控制PWM波形来驱动电动机,实现无刷直流电动机的平稳运转。近年来,随着工业的快速发展,对产品性能的

关键字:

DSP MOSFET

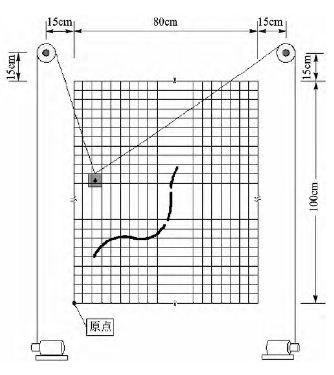

随着32位DSP的普及,32位处理器已经成为控制领域的主流产品,与传统的微处理器相比速度更快、性能更强、资源丰富,更符合发展的脚步。TMS320F28027是一款32位的DSP,具有运算速度快、稳定性高的优点。本文利用TMS320F28027控制两个步进电机,从而使物体在平面内运动,实现物体在平面内可以任意地画指定的曲线和圆等。图1为悬挂系统的模型。

1系统总体方案的设计

图2为悬挂系统控制框图,以TMS320F28027为控制芯片,利用L298N驱动两个步进电机。步进电机采用42HS48

关键字:

DSP L298N

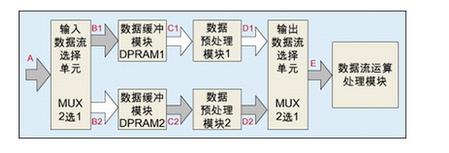

今天给大家带来的是我们在FPGA设计中经常要遇到的设计技巧与思想,即乒乓操作,串并转换,流水线操作和跨时钟域信号的同步问题。

之前也看过一些书,也在网上找过一些资料,不过小墨发现大部分都是理论讲解,仅仅是给一个框图就没事了,或者是好几个网站的资料都是一样的,都是复制的一个地方的,仅仅是讲解,没有实例,要不就是某个网站提供源码,但是要注册,还要花什么积分,没有积分还得要钱...很不利于初学者的学习(人与人之间怎么就不能多点信任呢~还要钱...)。所以小墨想写这么一篇文章来介绍一下这4种思想,理论部

关键字:

FPGA 可编程逻辑设计

一、为啥别忘了我

嵌入式逻辑分析仪—SigbalTap II,是Altera Quartus II 自带的嵌入式逻辑分析仪,与Modelsim软件仿真有所不同,是在线式的仿真,更准确的观察数据的变化,方便调试。

很多学过单片机的孩子认为,单片机可以在线单步调试,而FPGA是并发的,不能单步调试,这使得FPGA的调试学习带来了困难。其实这个说法不是完全正确的。别忘了,还有SignalTap II Logic Analyzer。有了这个嵌入式逻辑分析仪,在调试多通道或单通道数据,进

关键字:

FPGA SignalTap

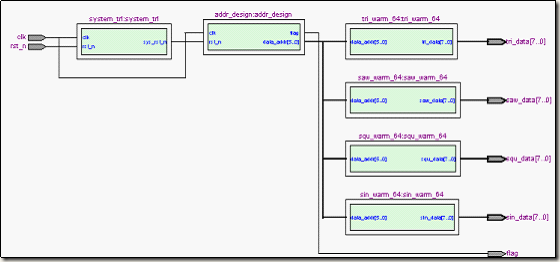

信号发生器又称为波形发生器是一种常用的信号源并且广泛应用于电子电路、通信、控制和教学实验等领域的重要仪器之一。为了降低传统函数信号发生器成本,改善信号发生器低频稳定性。笔者结合FPGA和51单片机产生0.596 Hz频率精度函数信号。笔者设计通过51单片机控制函数信号类型以及相关参数,用户可通过按键设置需要的波形、波形幅度、波形频率以及方波的占空比、相位。本文设计方案不仅具有良好的经济前景,也可以为当代高等教育深化改革做一个参考方向。

1 系统设计方案

1.1 系统硬件设计

本文中设

关键字:

FPGA 51单片机

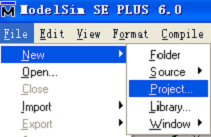

7.3 ModelSim的仿真流程

7.3.1 ModelSim的安装

ModelSim的最新版本可以从互连网上免费得到,需要购买的只是License文件。ModelSim的下载地址为http://www.model.com/。打开网站页面后可以点击Download,用户填写完一张表格以后可以得到一个小时的下载时间。

获得License的方法有很多种。

首先可以在线申请License文件,选取“开始→程序→ModelSim SE 5.8c&rar

关键字:

FPGA ModelSim

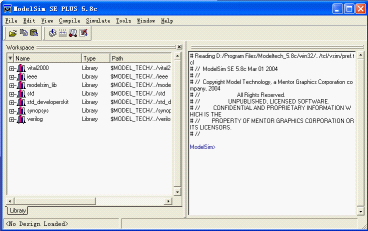

7.2 ModelSim仿真工具简介

ModelSim是Model Technology(Mentor Graphics的子公司)的DHL硬件描述语言的仿真软件,该软件可以用来实现对设计的VHDL、Verilog或者是两种语言混合的程序进行仿真,同时也支持IEEE常见的各种硬件描述语言标准。

无论从友好的使用界面和调试环境来看,还是从仿真速度和仿真效果来看,ModelSim都可以算得上是业界最优秀的HDL语言仿真软件。它是惟一的单内核支持VHDL和Verilog混合仿真的仿真器,是做FPG

关键字:

FPGA ModelSim

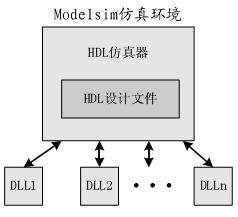

1、Modelsim 及 FLI接口介绍

Modelsim是 Model Technology(Mentor Graphics的子公司)的 HDL 硬件描述语言仿真软件,可以实现 VHDL, Verilog,以及 VHDL-Verilog 混合设计的仿真。除此之外,Modelsim还能够与 C 语言一起实现对 HDL 设计文件的协同仿真。同时,相对于大多数的 HDL 仿真软件来说,Modelsim 在仿真速度上也有明显优势。这些特点使 Modelsim 越来越受到 EDA设计者、尤其是 FPGA

关键字:

Modelsim FPGA

信号发生器是一种能提供各种频率、波形和输出电平电信号的设备。在测量各种电信系统或电信设备的振幅特性、频率特性、传输特性及其它电参数时,以及测量元器件的特性与参数时,用作测试的信号源或激励源。

无线电导航数字信号源的系统设计,完整参考方案

本无线电导航数字信号源总体设计思想采用直接数字频率合成器(DDS)技术,设计精确的时钟参考源精度、频率和相位累加器字长和正弦波函数表,实现研制技术要求的输出频率变化范围、频率变化步长和频率精度的调制正弦信号形式。

基于DDFS的程控音频仪器测试信号源

关键字:

无线电 FPGA

引言

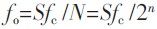

近年来电子信息技术飞速发展,使得各领域对信号源的要求不断提高,不但要求其频率稳定度和准确度高,频率改变方便,而且还要求可以产生任意波形,输出不同幅度的信号等。DDFS技术是自上世纪70年代出现的一种新型的直接频率合成技术。DDFS技术是在信号的采样定理的基础上提出来的,从“相位”的概念出发,进行频率合成,不但可利用晶体振荡的高频率稳定度、高准确度,且频率改变方便,转换速度快,便于产生任意波形等,因此,DDFS技术是目前高精密度信号源的核心技术。

1 DDFS技

关键字:

FPGA DDFS

dsp+fpga介绍

您好,目前还没有人创建词条dsp+fpga!

欢迎您创建该词条,阐述对dsp+fpga的理解,并与今后在此搜索dsp+fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473