当一辆汽车的性能不再由发动机排量决定,而是取决于车载芯片的算力与软件的智能程度,这场由" 软件定义汽车"(SDV)引发的产业革命已势不可挡。在2025 年CES 展会上,全球科技巨头纷纷亮出面向未来十年的智能汽车解决方案,而在这场技术竞速中,芯片架构的创新与人工智能的深度应用正在重塑整个汽车产业链。在这个背景之下,EEPW 与Imagination 的高级产品总监Rob Fisher进行了深度的交流采访,揭示了这场变革背后的技术逻辑与产业图景。Imagination 高级产品总监Rob

关键字:

202503 Imagination 软件定义汽车 GPU IP

轻量化TCP/IP(lwIP)堆栈是TCP/IP协议的精简实作,专门设计用来缩减RAM内存的使用量,这使其非常适合用在嵌入式系统。它提供三种独特的应用程序编程接口(API):‧ 未封装的低阶API‧ 负责网络通讯的高阶 API‧ BSD 风格的socket套接字 API本文专注探讨使用未封装API接口的范例。运用未封装API建置callback回调函数的应用程序会由核心事件触发。尽管未封装API较socket套接字API更为复杂,但由于其处理负荷(overhead)较低,因此能提供高出许多的吞吐量。接着将

关键字:

lwIP TCP/IP 堆栈整合 嵌入式应用 ADI

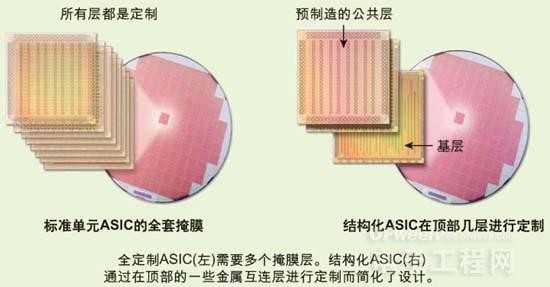

据报道,英伟达(NVIDIA)已开始关注"定制芯片"制造,该公司招募了数名台湾工程师,通过新建的台湾研发中心实施 ASIC 制造,促进本地人才的发展,并开拓这一细分市场。英伟达(NVIDIA)致力于开发定制芯片(ASIC)的消息一直不绝于耳,这主要是因为多家科技公司都希望拥有自己的人工智能算力储备,并根据自身需求量身定制。

目前,NVIDIA 开发的是开放架构的人工智能产品,如 Blackwell 和 Hopper

系列,但在为客户打造定制化解决方案方面,该公司仍在不断追求。

关键字:

NVIDIA 定制芯片 ASIC 制造 人工智能

国泰君安证券研报认为,ASIC(专用集成电路)针对特定场景设计,有配套的通信互联和软件生态,虽然目前单颗ASIC算力相比最先进的GPU仍有差距,但整个ASIC集群的算力利用效率可能会优于可比的GPU,同时还具备明显的价格、功耗优势,有望更广泛地应用于AI推理与训练。看好ASIC的大规模应用带来云厂商ROI提升,同时也建议关注定制芯片产业链相关标的。AI ASIC具备功耗、成本优势,目前仍处于发展初期,市场规模有望高速增长。

关键字:

AI ASIC

作为国产IC设计产业链中不可或缺的一环,国产IP授权厂商的不断涌现能够非常有效地提升国产IC设计产业的整体技术实力和行业竞争力。在ICCAD 2024上,5家领先的国产IP授权企业先后亮相,芯原微电子创始人、董事长兼总裁戴伟民,芯来科技创始人胡振波,锐成芯微CEO沈莉,奎芯科技联合创始人唐睿以及芯耀辉副总裁何瑞灵分别带来关于国产IP授权业务发展的介绍,为众多国内IC设计企业提供了开发高性能IC设计的技术底座。 作为一家成立不到五年的IP领军企业,芯耀辉专注于先进半导体IP研发和服务,凭借强大的自主研发能力

关键字:

芯耀辉 IP 路径依赖

摘要:● 新思科技超以太网IP解决方案将提供高达1.6 Tbps的带宽,可连接多达一百万个端点。● 新思科技UALink IP解决方案将提供每通道高达200 Gbps的吞吐量,连接多达 1024 个加速器。● 全新超以太网和UALink IP是基于新思科技业界领先的以太网和PCIe IP研发的,这些 IP 共同实现了5000多例成功的客户流片。● AMD、Astera Labs、Juniper Networks

关键字:

新思科技 大规模AI加速器集群 超以太网 UALink IP

芯原股份近日宣布推出全新Vitality架构的图形处理器(GPU)IP系列,具备高性能计算能力,广泛适用于云游戏、AI PC、独立显卡和集成显卡等应用领域。芯原新一代Vitality GPU架构显著提升了计算性能,并支持多核扩展,以进一步提升性能。该GPU架构集成了诸多先进功能,如一个可配置的张量计算核心(Tensor Core)AI加速器和一个32MB至64MB的三级(L3)缓存,提供强大的处理能力和出色的能效表现。此外,Vitality架构可单核支持多达128路云游戏,满足高并发和高画质的云端娱乐需求

关键字:

芯原 Vitality架构 GPU IP

无论是在出货量巨大的消费电子市场,还是针对特定应用的细分芯片市场,差异化芯片设计带来的定制化需求也在芯片设计行业中不断凸显,同时也成为了芯片设计企业实现更强竞争力和更高毛利的重要模式。所以,当您在为下一代SoC、ASIC或FPGA项目采购设计IP,或者寻求更适合的验证解决方案(VIP),以便更快更好地完成您的芯片设计项目的时候,SmartDV都可以快速且可靠地在其多元化的产品组合之上进行IP定制,以满足您期待的差异化设计需求。当大型IP供应商将其客户锁定在使用商品化的通用内核时,SmartDV就已经提供了

关键字:

IP Your Way SmartDV 定制IP

本系列文章从数字芯片设计项目技术总监的角度出发,介绍了如何将芯片的产品定义与设计和验证规划进行结合,详细讲述了在FPGA上使用硅知识产权(IP)内核来开发ASIC原型项目时,必须认真考虑的一些问题。全文从介绍使用IP核这种预先定制功能电路的必要性开始,通过阐述开发ASIC原型设计时需要考虑到的IP核相关因素,用八个重要主题详细分享了利用ASIC IP来在FPGA上开发原型验证系统设计时需要考量的因素。同时还提供了实际案例来对这些话题进行详细分析。这八个主题包括:一款原型和最终ASIC实现之间的要求有何不同

关键字:

202411 FPGA FPGA原型 确认IP ASIC SmartDV

进入2024年,全球RISC-V社群在技术和应用两个方向上都在加快发展,中国国内的RISC-V CPU IP提供商也在内核性能和应用扩展方面取得突破。从几周前在杭州举行的2024年RISC-V中国峰会以及其他行业活动和厂商活动中,可以清楚地看到这一趋势。作为全球领先的IP供应商,SmartDV也从其中国的客户和志趣相投的RISC-V CPU IP供应商那里获得了一些建议和垂询,希望和我们建立伙伴关系携手在AI时代共同推动芯片产业继续高速发展。SmartDV也看到了这一新的浪潮。上一次在行业庆祝RISC-V

关键字:

智权 SmartDV RISC-V CPU IP

本系列文章从数字芯片设计项目技术总监的角度出发,介绍了如何将芯片的产品定义与设计和验证规划进行结合,详细讲述了在FPGA上使用IP核来开发ASIC原型项目时,必须认真考虑的一些问题。文章从介绍使用预先定制功能即IP核的必要性开始,通过阐述开发ASIC原型设计时需要考虑到的IP 核相关因素,用八个重要主题详细分享了利用ASIC IP来在FPGA上开发原型验证系统设计时需要考量的因素。在上篇文章中,我们分享了第五到第六主题,介绍了我们如何确保在FPGA上实现所需的性能和在时钟方面必须加以考量的因素有哪些。本篇

关键字:

202409 ASIC IP核 FPGA SmartDV

本系列文章从数字芯片设计项目技术总监的角度出发,介绍了如何将芯片的产品定义与设计和验证规划进行结合,详细讲述了在FPGA上使用IP核来开发ASIC原型项目时,必须认真考虑的一些问题。文章从介绍使用预先定制功能即IP核的必要性开始,通过阐述开发ASIC原型设计时需要考虑到的IP核相关因素,用八个重要主题详细分享了利用ASIC IP来在FPGA上开发原型验证系统设计时需要考量的因素。在上篇文章中,我们分享了第二到第四主题,介绍了使用FPGA进行原型设计时需要立即想到哪些基本概念、在将专为ASIC技术而设计的I

关键字:

ASIC IP FPGA SmartDV

摘要:● 新思科技ARC HS4xFS处理器IP和新思科技IP开发流程均通过独立审计机构SGS-TṺV Saar的ISO/SAE 21434认证。● 获得ISO/SAE 21434认证可应对不断变化的网络安全威胁,有助于在整个生命周期内为汽车系统提供长期的安全性与可靠性。● 经过安全风险分析(SRA)认证的新思科技ARC HS4xFS处理器IP助力开发者能够以安全的方式将IP集成到系统中,从而满足ISO/SAE 21434要求。●&n

关键字:

新思科技 ISO/SAE 21434 网络安全合规认证 IP 汽车安全

本系列文章从数字芯片设计项目技术总监的角度出发,介绍了如何将芯片的产品定义与设计和验证规划进行结合,详细讲述了在FPGA上使用IP核来开发ASIC原型项目时,必须认真考虑的一些问题。文章从介绍使用预先定制功能即IP核的必要性开始,通过阐述开发ASIC原型设计时需要考虑到的IP核相关因素,用八个重要主题详细分享了利用ASIC所用IP来在FPGA上开发原型验证系统设计时需要考量的因素。在上篇文章中,我们介绍了将ASIC IP移植到FPGA原型平台上的必要性,并对原型设计中各种考量因素进行了总体概述,分析开发A

关键字:

ASIC IP FPGA SmartDV

一站式定制芯片及IP供应商——灿芯半导体(上海)股份有限公司近日宣布成功研发出一款通用高性能小数分频锁相环(fractional-N PLL) IP,支持24bits高精度小数分频,最高输出频率4.5Ghz,另外还支持扩频时钟(SSC)功能,可以为客户提供多功能的小数分频 PLL解决方案。PLL电路一般用于产生输出频率,输出频率值与PLL的参考输入频率呈倍数关系。小数分频PLL通过频率乘法比例的小数值,实现更精确的输出频率控制,从而提供更高精度和准确度的输出频率。SSC发生器是在一定频率范围内调制时钟信号

关键字:

灿芯半导体 小数分频 锁相环 IP

asic ip介绍

您好,目前还没有人创建词条asic ip!

欢迎您创建该词条,阐述对asic ip的理解,并与今后在此搜索asic ip的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473