数字化全双工语音会议电路(06-100)

——

基于FPGA的全双工语音会议电路

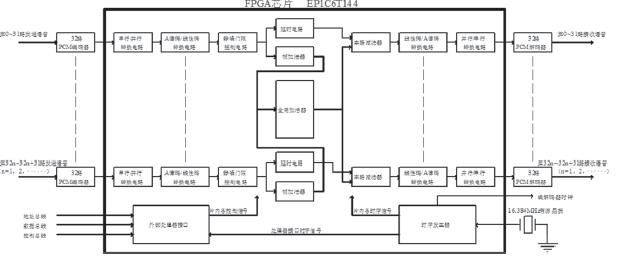

本文引用地址:https://www.eepw.com.cn/article/81181.htm 图1即为基于FPGA的数字化全双工语音会议电路的原理框图。

图1中间框内的电路全部由一片FPGA芯片来实现。模拟语音信号通过PCM编码器成为串行数字语音信号送入FPGA芯片。PCM语音编码以32个时隙组成1帧,每路语音占用1个时隙。为了发挥FPGA并行处理信号的长处,把输入语音信号每32路作为1组,经编码后成为1帧PCM信号,FPGA对各帧信号进行并行处理。例如输入是128路语音时,FPGA就同时处理4帧PCM信号。经FPGA处理后的信号最终仍然分帧输出,经PCM解码器后还原为模拟语音。图中为了说明信号流程把PCM编码器和解码器分开来画,实际上编解码器是集成于同一芯片内的。

以下简要说明FPGA内各电路模块的功能:

串行/并行转换电路

输入到FPGA的串行PCM信号通过该电路将每时隙8比特的串行数据转换成8位的并行信号,然后暂存在用FPGA片内RAM资源设计成的双端口存储器中。双端口存储器的另一端按要求的时序依次输出各并行数据,供后续处理。

A律码/线性码转换电路

本部分电路完成8位A律PCM码到13位线性码的转换,以便随后对语音进行线性运算。转换电路用AHDL语言编写。在每帧的125μs时间内32路PCM语音信号分时使用本电路,因此每32路可共用1个码型转换电路。

评论