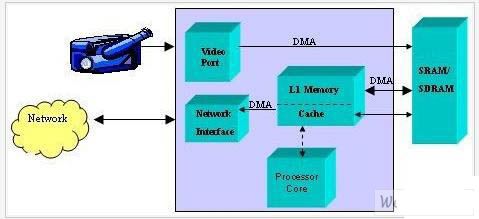

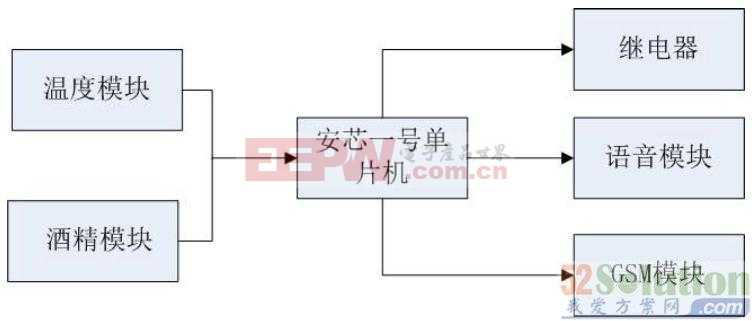

基于单片机系统采用DMA块传输方式实现高速数据采集

3.2 数据线与地址线的控制

总线的选择控制由DMA允许信号控制两组74HC245三态总线收发器,使其分别处于开通和高阻状态。此两组总线收发器一端并接至RAM,另一端分别接单片机系统总线和A/D转换外部总线。当DMA禁止周期时DMA允许信号为低,选通系统总线允许单片机对RAM进行读写操作。反之当DMA周期时DMA允许信号为高,选通外部总线允许DMA控制器对RAM写操作。数据线有8根(D0~D7),对数据线的切换需要两片74HC245,而地址线有16根(A0~A15),切换地址线需要4片74HC245才可以。另外还需两片用以对RAM的读写线的切换,对读写线的控制采用相同的方法,也是由DMA允许进行两周期的控制权切换。

3.3 DMA块数据传输

与非门输出1MHz的振荡信号,连接A/D芯片/RD脚,在低电平开始时已采集的数据被输出到数据线。地址计数器被设计为下降沿触发,因此下降沿开始后地址计数器将在预设的起始地址的基础上加1,形成新的地址输出至地址线。数据和地址的形成均在下降沿后的160ns(由74HC系列计数器性能参数可知其最大传输延迟时间为40ns,有四片级连总计160ns。由MAX153CPP的手册可知其读写模式下Data-AcceessTime为160ns)内完成,其小于振荡信号低电平停留时间500ns。在下一个振荡的下降沿到来之前数据地址保持不变,在此后的上升沿时数据被写入RAM的指定地址,第二个下降到来后重复这样的过程,地址计数器加1形成新的地址和读出A/D转换器中新的数据,再写入储存器。工作时序参见图4。

3.4 响应过程的结束

DMA过程的结束设计在地址溢出时。设计利用地址计数器的溢出位,当地址溢出即大于(FFFF)H时溢出位为1,经反向器反向后至四输入端与非门的输入端,使其输出常为高而达到封锁的目的。直到单片机系统重新初始化地址计数器,清溢出标志,并重新DMA允许后才能再次进入DMA准备就绪状态。

4 软件设计(主流程)

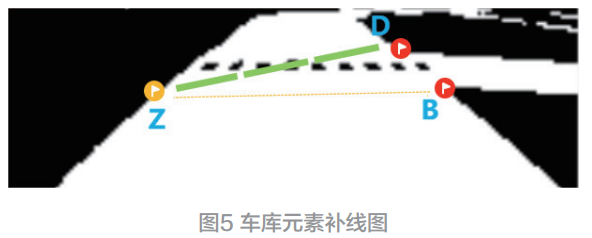

主程序流程图见图5。

单片机系统以其方便、简洁、灵活、廉价为主要特点,所以在DMA电路设计中一定要结合实际应用简化设计,软件硬件综合设计避免系统过于复杂,才能达到优质廉价的最终目的。利用本设计研制的数字式磁通表综合性能达到了预期指标,并获得满意的性能价格比

评论