PFC控制器芯片内部剖析

pfc控制器的架构

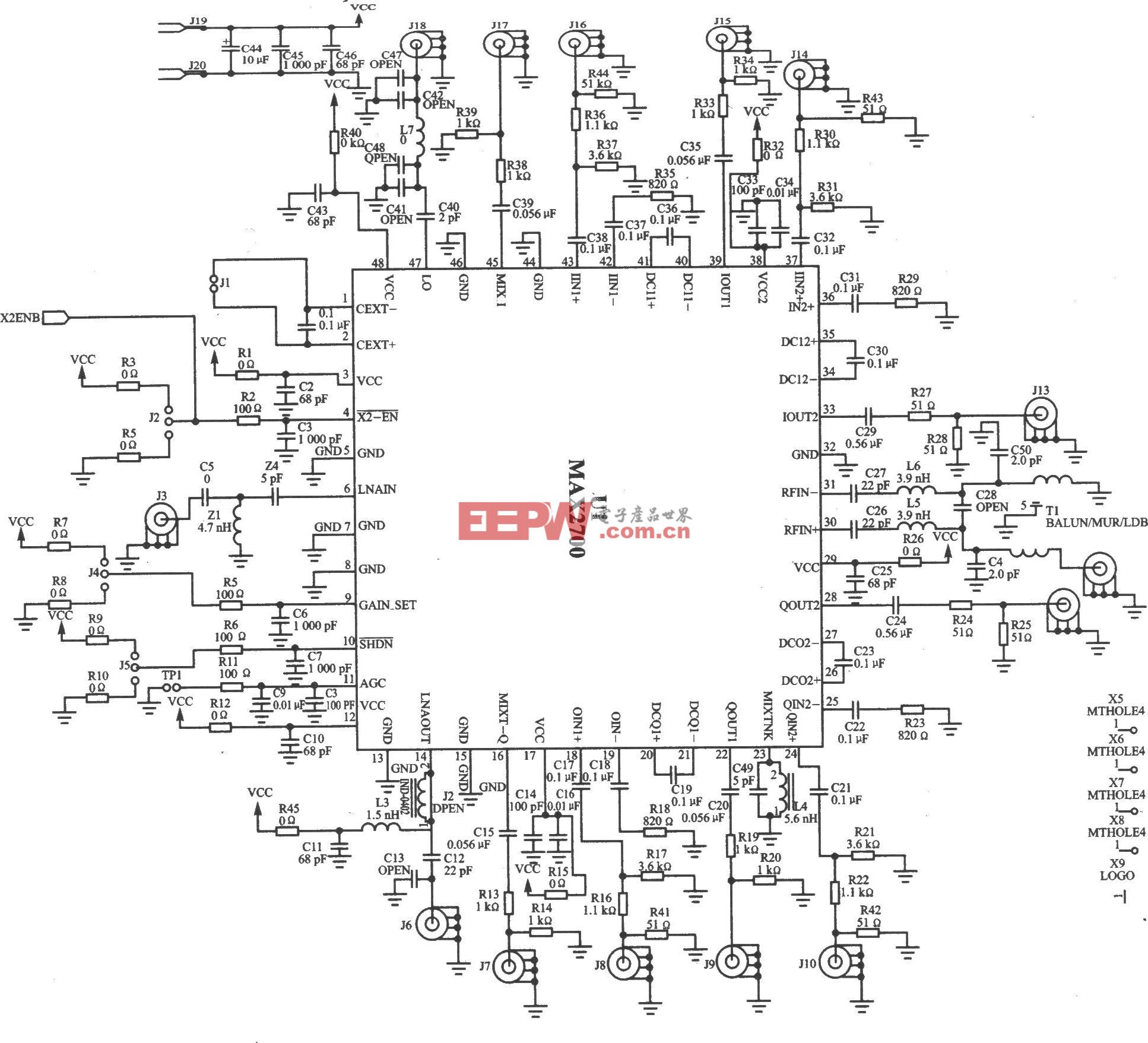

本文引用地址:https://www.eepw.com.cn/article/20832.htm尽管有许多公司在生产不同类型的pfc (power factor correction,pfc)控制器,这些芯片的架构和结构却极为类似。大多数pfc控制器都采用增益调制器、电流误差放大器 (iea)、pfc比较器、电压误差放大器 (vea) 和pfc脉冲输出驱动器。图1是pfc控制器的模块示意图。

内环是电流控制回路,包含了增益调制器、iea和pfc比较器。外环控制回路是电压控制回路,利用vea作为误差放大器。vea输出 (veao) 也是增益调制器的输入之一。内环电流控制回路修整来自交流线路的线电流,并与交流线电压成正比。外环电压回路调节pfc直流总线电压,使之保持在大约385v左右。需注意的是,与电压控制回路相比,电流控制回路的带宽要大得多。

pfc控制器的pfc比较器 驱动器部分在图1中以虚线标注,其设计围绕pfc比较器。振荡器产生锯齿波形及与该锯齿波形下降边缘同步的时钟 (clk) 信号。图1所见的锯齿波形被称为“pfc_ramp”信号,也即ramp1。

如图1所示,在周期开始处,clk信号为高时,pfc_out为低。一旦pfc_ramp超过电流误差放大器的输出 (ieao) 值,pfc_out就变高,最终接通外部pfc开关管。pfc_out一直保持高电平直到周期结束,clk会将它设为低电平。因此,pfc能实现尖端的调节功能。

通常,pfc芯片能确保pfc的负载周期d和pfc_out脉冲不会达到100%。防止了升压电感器达致饱和。最大的负载周期会在ac线电压的过零点处出现 (如图2所示的ch2)。

因此,当vin为零时,控制器芯片限制负载周期为98%。例如,图3所示是飞兆半导体的pfc控制器fan4810的实际波形。这里ch4是电流误差放大器的输出。

因此,当vin为零时,控制器芯片限制负载周期为98%。例如,图3所示是飞兆半导体的pfc控制器fan4810的实际波形。这里ch4是电流误差放大器的输出。

对设计人员而言,设置正确的电流误差放大器输出值是非常重要的。例如,fan4810规格定义ramp1谷对峰电压为2.5v。这意味着通过调节,ieao电压的动态范围应该在ramp1信号摆幅内,如图3所示的线迹ch1和ch4。

在许多ic中,iea是跨导放大器 (transconductance amplifier)。图1所示为围绕该放大器的2类补偿电路。该补偿电路与参考电压引脚vref连接,建立了pfc的软启动功能。当启动时,ieao上升到参考电压水平;随着回路进行调节,ieao从vref水平下降到工作水平。这保证了pfc的负载周期从0%

逐渐增加到回路所需要的数值,从而提供了软启动功能,如图4所示。

在许多ic中,iea是跨导放大器 (transconductance amplifier)。图1所示为围绕该放大器的2类补偿电路。该补偿电路与参考电压引脚vref连接,建立了pfc的软启动功能。当启动时,ieao上升到参考电压水平;随着回路进行调节,ieao从vref水平下降到工作水平。这保证了pfc的负载周期从0%

逐渐增加到回路所需要的数值,从而提供了软启动功能,如图4所示。 增益调制器的功能

增益调制器的功能

pfc控制器的中部心分是增益调制器和电压误差放大器,如图1所示。该增益调制器会生成控制信号给电流控制回路,让后者对这个输入电流进行修整。fan4810 pfc控制器的电流控制回路确保电流传感器的负反馈电压被内部rcp电阻上的正电压所平衡。这一正电压由流经rcp的增益调制器输出电流所生成。因此,所产生的线电流 (i_line) 和 isense 引脚上的电压被迫重复增益调制器输出波形的形状。换言之,这个情况:

i_line r_{s}=i_{gm} r_{cp} (1)

会常常出现。这里,rs代表线电感电阻 (line current sense resistor),而igm是增益调制器的输出电流。

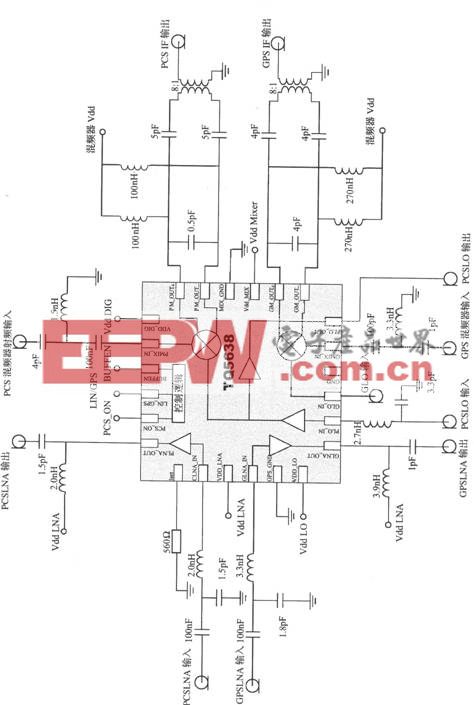

为了修整产生的线电流,增益调制器采用三个输入:iac、vrms 和vea输出。引脚iac通过1m 电阻与ac线整流桥的输出相连接 (见图6中的r4)。iac为两倍线频率全波整流正弦波,与瞬态ac线电压成正比。iac实际上修整了增益调制器输出电流,该电流由下式的正弦曲线描述:

为了修整产生的线电流,增益调制器采用三个输入:iac、vrms 和vea输出。引脚iac通过1m 电阻与ac线整流桥的输出相连接 (见图6中的r4)。iac为两倍线频率全波整流正弦波,与瞬态ac线电压成正比。iac实际上修整了增益调制器输出电流,该电流由下式的正弦曲线描述:

i_{gm}=frac{i_{vc} v_{rao}}{v_{rms}^{2}} (2)

在vrms引脚的电压是与ac线电压rms值成正比的dc电压,如图6所示。igm 的设计与vrms平方成反比。

为什么增益调制器的输出电流必须与ac线电压rms 值的平方成反比呢?假设veao恒定不变,如果输入线电压加倍,为提供相同的功率,那么输入电流及igm就应相应减小一半。由式 (2) 可知,若线电压加倍,iac也会加倍。因此要抵消iac 的增大,vrms信号便应增加4倍。

vea带宽和thd

增益调制器的第三个输入是vea输出,会决定增益调制器输出电流的幅值。vea的输入与监测pfc输出电压的分压器相连接 (图6)。在fan4810的例子中,fb引脚在额定总线电压 (nominal bus voltage) 时被设置为2.5v。vea是带类2补偿电路的跨导放大器,如图1所示。要关闭vea的反馈回路,有两个相互矛盾的要求:1) 回路应具有足够低的带宽来缓减dc总线上的120hz 纹波电压,从而减小输入线电流的总谐波失真 (total harmonic distortion,thd);2) 回路必须足够快的负载瞬态响应。

thd是设计人员考虑的重要因素。由于输出电容的移相特性,大容量电容的电压纹波相位与线电压相比时 (见图3中的ch 3) 位移了90度。因此与位移的电压纹波成正比的信号直接输入到vea,放大器的增益和带宽应该受到限制。通常,电压控制回路分频频率设置在10 ~30hz之间。

增益调制器有两个有趣的特性很少被提及。首先,转移特性提供了自然的电压过低保护 (brown out protection)。增益调制器的最大增益被设计在最小线电压处。若输入电压恰巧低于规定的最小值 (电力减弱情况),那么增益和pfc负载周期都会急剧下降,因而降低总线电压。第二个有趣的特性是内置过电流保护功能。增益调制器的最大输出电压会被限制,在fan4810中为0.8v。如果因为任何原因,例如由于过载,isense 引脚上的电压下降到低于 0.8v,iea的反相输入对地负值将会更大。因此,ieao水平将增加,这会降低pfc负载周期和总线电压,从而限制输出功率 (见图1)。

pfc保护电路

如同其他控制器一样,fan4810包括了大量与pfc工作相关的保护电路。其中有过电压保护 (over-voltage protection,ovp) 和过电流保护 (over-current protection,ocp) (见图5)。利用由pfc ovp或电流限值设置的sr触发来终止pfc输出脉冲。所以,ovp和ocp故障会在每一个周期中被监测及闩锁。

飞兆半导体器件具有“三重故障 (tri-fault)”保护功能。这种保护可覆盖以下故障:(a) fb引脚对地短路,(b) 从pfc dc总线分压器到芯片的vfb引脚的连线 (引线或pcb走线) 断裂,(c) 分压器的顶端或底部电阻开路 (图6中的电阻r1、r2)。如果fb对地短路 (情况(a)),pfc_fb引脚上的电压将低于0.5v,tri-fault 比较器输出将停顿pfc out脉冲。在引线断裂(情况(b)) ,内部电流源开始对电容ctf充电。于是,一旦fb引脚上的电压超过2.75v,ovp比较器将终止pfc输出。电容ctf (图6中的c2) 是可选的选项,定义时间t_f 来触发保护电路。

t_f=frac{ctf 2.75v}{200na}

对于 (c) 的故障情况,ovp或tri_fault将终止pfc_out脉冲。如果因任何原因dc总线电压超过额定水平的10%,ovp保护开始起作用。例如,若额定总线电压为385vdc (fb引脚为2.5v),只要总线电压超过423vdc (fb引脚为2.75v),ovp就会被触发。

小结

pfc控制器集成了诸如过电压保护 (ovp)、过电流保护 (ocp) 及fan4810示例中的三重故障 (trifault) 保护等功能,在ac/dc设计中起着重要的作用。带有有源pfc及接近统一功率因子的转换器能满足ice61000-3-2 规范的要求,减少了电源设计者的一个主要顾虑。

评论