放大器实用设计案例精华汇总(一)

![]()

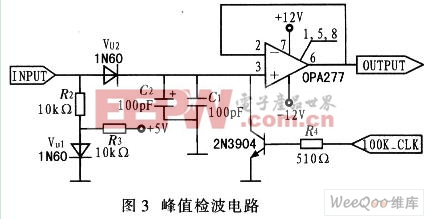

4.2 峰值检波电路

峰值检波电路由二极管电路和电压跟随器组成。其工作原理:当输入电压正半周通过时,检波管 VU2导通,对电容C1、C2充电,直到到达峰值。三极管的基极由FPGA控制,产生1Oμs的高电平使电容放电,以减少前一频率测量对后一频率测量的影响,提高幅值测量精度。其中Vu1为常导通,以补偿VU2上造成的压降。适当选择电容值,使得电容放电速度大于充电速度,这样电容两端的电压可保持在最大电压处,从而实现峰值检波。

该电路能够检测宽范围信号频率,较低的被测信号频率,检波纹波较大,但通过增加小电容和大电容并联构成的电容池可滤除纹波。而后级隔离,则增加由OPA277构成的射极跟随器,如图3所示。

5 系统软件设计

5.1 程序部分设计

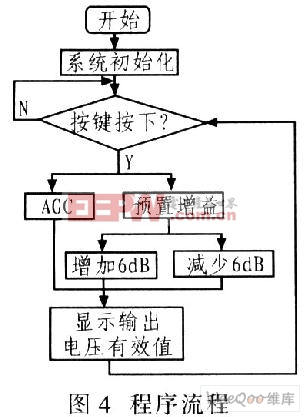

系统软件设计遵循结构化和层次化原则,由一个主程序及若干子程序构成。主程序通过调用子程序控制子程序间的时序,从而使整个程序正常运行。系统软件设计部分由单片机和FPGA组成。单片机主要完成读取键值、控制增益和显示功能。而FPGA则作为总线控制器,管理键盘、液晶和A/D转换器与单片机之间的数据交换。以Ouartus II 7.2为设计环境,用Verilog HDL硬件描述语言编程,完成各功能模块的设计,并仿真测试设计好的各个模块,再将各个模块相互连接。程序以按键中断为主线,以各项功能为分支,图4为程序流程。

5.2 FPGA部分设计

FPGA主要完成A/D、D/A转换器的串并转换。采用12位D/A转换器TLV5618,该器件是串行接口,大大节约系统端口资源,但MCU的P0、 P2端口是并行口,与串行器件的时序匹配较复杂,用静态口P1端口模拟串行口时序又会占用MCU很多处理时间,影响系统效率。

为使MCU对串行器件操作简单,把串行时序在FPGA中用状态机描述,同时该控制状态机又对MCU提供P0口、CS、WR的微机标准时序接口形式,这样MCU只需选中相应地址,就可写入所要得到的电压数据,状态机会完成串并转换。

以串行接口时序将数据写入器件并锁存,与写IO端口操

电子管相关文章:电子管原理

评论