双DSP柔性处理系统研究

为了实现图像的实时采集与高速处理,本系统用两片双口RAM组成相互独立的视频缓存,分别对应主/从DSP处理器。设计时选用IDT公司的3.3V 异步双口PRAM IDT70V657,同时与DSP接口采用ASRAM方式。由于EMIF的ASRAM接口支持32Bit的数据接口,因此,利用IDT70V657构成不完全地址结构来存取数据能够更好地实现8Bit锁存数据与C6414的接口,而无须对DPRAM进行宽度扩展。同时亦可减少DSP读取外部数据的时间开销。

IDT70V657的大小是32K×36Bit系统采用将两个DPRAM各划分为前后两个半场的方式来实现存取数据时的乒乓切换。即在系统工作的任一时刻,当对DPRAM前半场写入数据时,使DPRAM后半场向DSP读出数据。当前半场写满视频数据时,由FPGA给DSP发出中断信号,以通知DSP读出DPRAM前半场所写入数据,同时,将A/D转换器的数据写入DPRAM后半场缓冲空间,如此反复进行来实现数据的读出与写入同步操作。

b. 双DSP高速信号处理系统

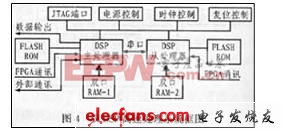

TMS320C6414-600型DSP的主频高达600MHz,在超高速实时图像处理领域有着非常出色的性能。本系统的双DSP高速实时信号处理系统就以2片C6414-600 DSP芯片为核心组成邻域图像并行处理机,并通过系统任务的划分与分解实现同步并行运算处理。其系统框图如图4所示。

在本系统中,主DSP完成的主要功能如下:

(1) 实现外部缓存数据到片内的搬移,为DSP高速批处理开辟片内二级缓存;

(2) 实现与外部上位机的即时通讯,接收外部命令与目标参数;

(3) 实现与从DSP的即时通信,下传命令字与目标参数以及获取中间结果;

(4) 运行系统跟踪算法,承担系统核心运算任务的一半;

(5) 与FPGA建立即时通信,实现系统程序模块的调度与协调;

从DSP完成的主要功能是:

(1) 实现外部缓存数据到片内的搬移,为DSP高速批处理开辟片内二级缓存;

(2)运行系统跟踪算法,承担系统核心运算任务的一半;

(3)实现与主DSP的即时通信,上传匹配运算中间结果;

评论