英伟达——推理王国持续扩张

英伟达通过极致协同设计,每年从芯片、机柜到人工智能工厂,持续释放颠覆性技术优势

(注:文中涉及的英伟达产品代际与技术规格图表,已在翻译中转化为清晰的文字说明与表格,核心参数完整保留)

在 2026 年 GPU 技术大会(GTC)上,英伟达发布了一系列突破性成果,创新步伐丝毫未减。本次大会推出三款全新系统:Groq LPX、Vera ETL256 与 STX;同时公布 Kyber 机柜架构的重大更新,首次展示面向规模化扩展网络的共封装光学(CPO)技术,推出 Rubin Ultra NVL576 与 Feynman NVL1152 多机柜系统,并披露 Feynman 架构的早期细节。黄仁勋在主题演讲中重点提及的 InferenceX 技术,成为本次大会的一大亮点。

本文将为你复盘 2026 年 GTC 大会核心内容,解答英伟达尚未明确的关键问题:深入解析 LPX 机柜与 LP30 芯片,阐释注意力与前馈网络解耦(AFD)技术原理;详解 NVL144、NVL576、NVL1152 背后的机柜架构差异,说明光模块的部署规模及高密 Vera ETL256 的设计逻辑;揭秘下一代 Kyber 机柜的重大更新与隐藏细节。

一、Groq 收购与 LPU 技术解析

近期人工智能基础设施领域最重大的事件之一,便是英伟达对 Groq 的 “收购”—— 严格来说,英伟达以 200 亿美元的价格获得 Groq 的 IP 授权,并吸纳其核心团队。这一交易形式虽未构成法律意义上的完全收购,却实质达到收购效果,既简化了监管审批流程(若按完全收购提交反垄断审查,大概率无法通过),又避免了冗长的交割周期,让英伟达迅速获得 Groq 的技术与人才。这也是为何交易宣布后不到四个月,英伟达便推出整合 Groq 技术的系统概念,并将其融入 Vera Rubin 推理架构。

1. LPU 架构核心原理

Groq 的 LPU(推理处理单元)架构最早在 2020 年国际计算机体系结构研讨会(ISCA)上披露。与传统多通用核心互联架构不同,LPU 将硬件重新设计为多个专用功能单元组(称为 “切片”),单元组间通过流寄存器、暂存 SRAM 实现数据交互。Groq 采用单级暂存 SRAM 而非多级存储层级,确保硬件执行的确定性。

LPU 架构包含四类切片:

VXM 切片:负责向量运算

MEM 切片:负责数据加载 / 存储

SXM 切片:负责张量形状转换

MXM 切片:负责矩阵乘法运算

切片按水平方向布局,数据沿水平方向流转;切片内部,指令沿垂直方向在单元间传输,整体类似 “垂直传指令、水平传数据” 的脉动阵列结构。这种数据流与指令流设计需通过细粒度流水线实现高性能,而确定性计算特性让编译器可通过激进的指令调度与重叠,隐藏延迟。高带宽 SRAM 与激进流水线设计,是 LPU 实现低延迟的两大核心。

2. LPU 芯片迭代历程

第一代 LPU:基于格芯 14nm 工艺打造,由美满电子负责物理设计。2020 年流片时,14nm 工艺已相当成熟(同期主流人工智能芯片多采用台积电 N7 工艺),适合作为验证 Groq 架构的初代产品,更侧重架构差异化而非制程领先性。其核心优势是可完全在美国完成制造与封装,而竞争对手高度依赖亚洲供应链(中国台湾的逻辑芯片与封装、韩国的 HBM)。

第二代 LPU:原计划采用三星晶圆厂 SF4X 工艺,由三星奥斯汀工厂生产,延续 “美国本土制造” 的定位。三星为争夺先进制程客户,以优惠条款与投资吸引 Groq 合作,并参与了 Groq 2024 年 8 月的 D 轮融资及 2025 年 9 月英伟达 “收购” 前的最后一轮融资。但该产品因设计问题未能量产 —— 芯片上的 C2C 串并转换器(SerDes)无法达到宣传的 112G 速率,导致功能异常。

第三代 LPU(LP30):英伟达将量产的首款 LPU 产品,跳过第二代直接迭代。产品本身无英伟达设计参与,但已修复第二代的 SerDes 问题。后续还将推出小幅升级的 LP35 版本,仍基于 SF4 工艺,需重新流片,将支持 NVFP4 数据格式,为抢占上市时间,暂不做其他大幅设计改动。

第四代 LPU(LP40):将采用台积电 N3P 工艺与 CoWoS-R 封装,英伟达将深度参与设计,融入 NVLink 协议(替代 Groq 原生 C2C),并与 Feynman 平台深度协同。计划采用混合键合 DRAM 技术扩展片上内存, latency 与带宽略低于 SRAM,但远超传统 DRAM;SK 海力士将为其提供 3D 堆叠 DRAM。

3. SRAM 在存储层级中的定位

SRAM 的优势是低延迟、高带宽,但密度低、成本高。因此,以 Groq LPU 为代表的 SRAM 架构设备,首 token 生成速度与单用户每秒 token 生成量极快,但总吞吐量受限 —— 有限的 SRAM 容量易被权重占满,留给随用户批量增加而扩容的 KV 缓存空间有限。而 GPU 在吞吐量与成本上更具优势。

这也是英伟达决定整合两种架构的核心原因:将延迟敏感、内存需求较低的解码环节,交由低延迟、高 SRAM 占比的 LPU 处理;将内存密集型的注意力计算,交由具备大容量高速内存(虽不及 SRAM 快)的 GPU 完成,实现优势互补。

各类存储介质性能对比

存储类型 | 单 GPU/XPU/LPU 容量 | 单 GPU/XPU/CPU 带宽 | 延迟 |

HBM4 12 层堆叠 | 约 288GB | 约 22TB/s | 约 100-150 纳秒 |

DDR5 | 128-1024GB(2-16 条 DIMM) | 约 307-614GB/s | 约 60-100 纳秒 |

GDDR7 | 约 16-48GB(8-12 颗芯片) | 约 1.5-1.8TB/s | 约 50-80 纳秒 |

LPU SRAM | 约 500MB | 约 150TB/s | 约 5-20 纳秒 |

4. 第三代 LPU(LP30)核心规格

LP30 芯片采用接近掩模版尺寸的单片设计,无需先进封装,500MB 片上 SRAM 占用大量芯片面积,而矩阵乘法核心仅提供 1.2 PFLOPs 的 FP8 算力,远低于英伟达 GPU。相比第一代 LPU(230MB SRAM、750 TFLOPs INT8 算力),性能提升主要源于制程从格芯 14nm 迁移至三星 SF4 工艺。

采用 SF4 工艺的核心优势:不受台积电 N3 工艺产能限制(当前 N3 工艺制约加速器量产,是行业算力紧张的关键原因),且无需依赖同样紧缺的 HBM,让英伟达可在不占用宝贵的台积电产能与 HBM 配额的前提下,扩大 LPU 产量,创造独特的增量收入与产能优势。

二、GPU 与 LPU 整合:注意力与前馈网络解耦(AFD)

英伟达引入 LPU 的核心目标是提升高交互场景的推理性能,核心技术路径之一便是注意力与前馈网络解耦(AFD)—— 该技术最早在 MegaScale-Infer 与 Step-3 中提出。

1. LLM 推理的两个阶段

预填充(Prefill):处理完整输入上下文,属于计算密集型任务,适合 GPU 执行。

解码(Decode):逐一生成新 token,属于内存受限型任务,对延迟敏感。LPU 的高 SRAM 带宽与低延迟特性,可显著加速这一迭代过程。

2. 注意力与 FFN 的性能差异

注意力(Attention)与前馈网络(FFN)是模型中的两类核心运算:

注意力运算:输出需传入 token 路由器,路由器将每个 token 分配给 k 个专家(每个专家对应一个 FFN);解码阶段,注意力运算受 KV 缓存加载限制,批量扩大时 GPU 利用率提升有限。

FFN 运算:计算仅依赖 token 输入,无状态;批量扩大时 GPU 利用率提升更明显。

随着最先进的混合专家(MoE)模型稀疏度不断提高,token 可选择的专家池扩大,每个专家接收的 token 减少,导致利用率下降 —— 这正是 AFD 技术的核心应用场景。

3. AFD 技术原理

将注意力与 FFN 运算解耦,分别映射至不同硬件:

注意力运算→GPU:GPU 擅长处理动态工作负载,其 HBM 容量可完全分配给 KV 缓存,提升单次处理的 token 总量,进而提高每个专家的平均 token 处理量,改善利用率。

FFN 运算→LPU:LPU 架构具有确定性,更适合静态计算工作负载。

4. 令牌路由与通信优化

AFD 技术中,GPU 与 LPU 间的令牌路由可能成为瓶颈(尤其在严格延迟约束下),路由流程包含 “分发(dispatch)” 与 “合并(combine)” 两步:

分发:通过全对全(All-to-All)集合运算,将每个 token 路由至最优的 k 个专家。

合并:专家运算完成后,通过反向全对全集合运算,将结果返回至源 GPU,继续下一层计算。

为隐藏路由通信延迟,采用 “乒乓流水线并行” 技术:除将批量拆分为微批量并进行计算流水处理外,令牌在 GPU 与 LPU 间循环传输(类似 “乒乓”),最大化重叠计算与通信时间。

5. 推测解码(Speculative Decoding)

LPU 加速解码的另一路径是推测解码:在 LPU 上部署草稿模型(draft model)或多令牌预测(MTP)层。

核心原理:对于 N 个 token 的上下文解码,若新增 k 个 token(k<<N),延迟仅小幅增加。利用这一特性,草稿模型 / MTP 层先预测 k 个新 token(小模型解码延迟更低);主模型仅需对这 k 个 token 进行一次 “热身预填充” 验证,延迟相当于单次解码步骤。推测解码通常可将每步解码的输出 token 数提升 1.5-2 倍,而 LPU 的低延迟特性可进一步扩大延迟节省效果,提升吞吐量。

与 AFD 技术不同,推测解码中的草稿模型 / MTP 层需动态加载 KV 缓存(有状态),且模型体积达数十 GB(远超单个 FFN 的数百 MB)。为此,LPX 计算托盘的结构扩展逻辑 FPGA,可为 LPU 提供高达 256GB 的 DDR5 内存支持。

三、LPX 机柜系统

英伟达在 GTC 上展示的 LPX 机柜包含 32 个 1U LPU 计算托盘与 2 个 Spectrum-X 交换机,这一配置与收购前 Groq 的原始服务器设计高度相似,但预计 2026 年第三季度量产时将有调整。以下是量产版本的核心细节:

1. LPX 机柜整体配置

组件 | 规格 |

光纤跳线 / 交换面板 | - |

电源架 | 1U,90kW(共 4 个) |

带外管理交换机 | 1Gbe MGMT Switch 01 - SN2201 M DC |

机柜加固件 + 接水盘 | - |

计算托盘 | 2U,含 16 颗 Groq 3 LPU、2 颗 FPGA、1 颗 CPU(共 16 个) |

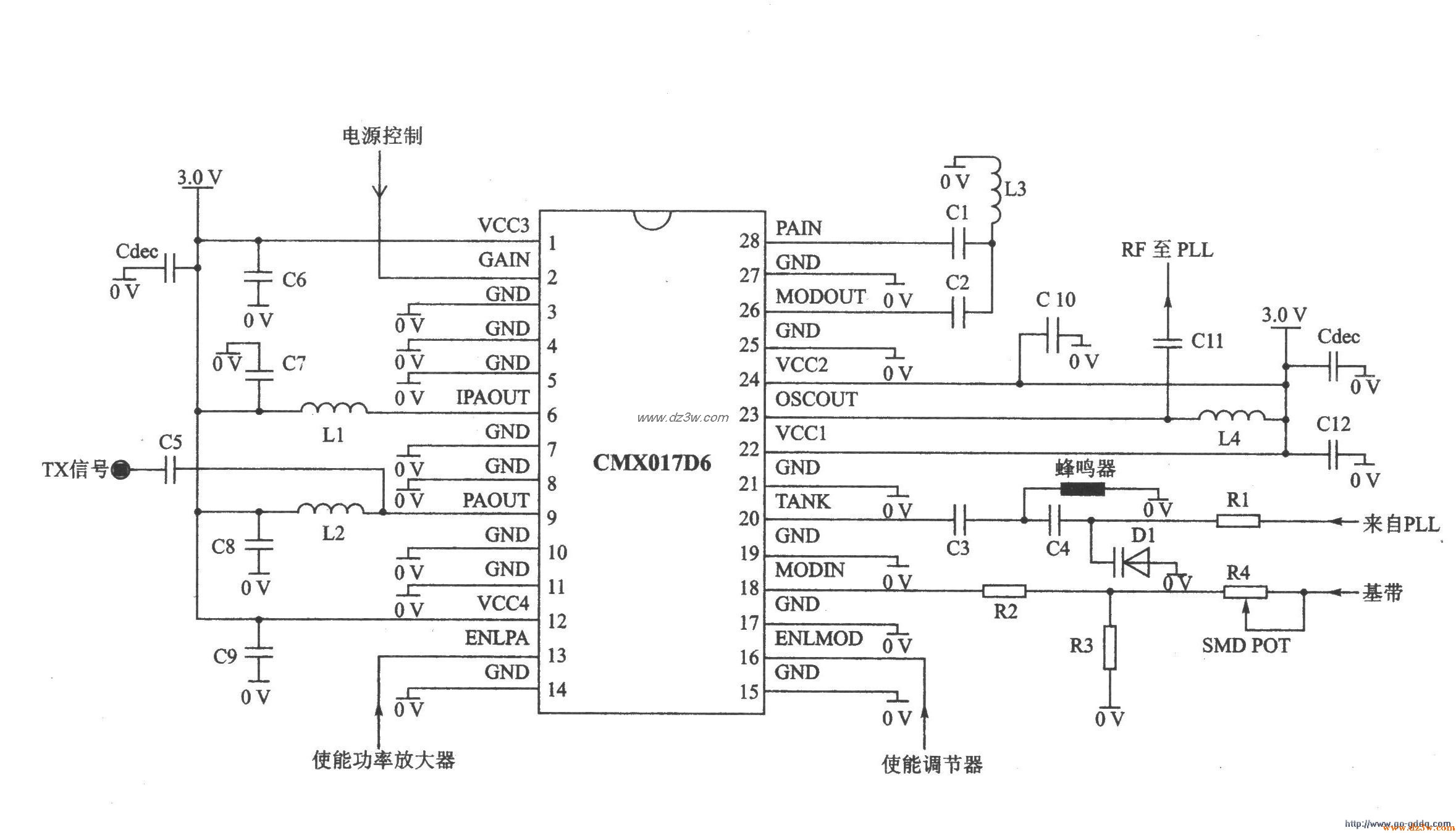

2. LPX 计算托盘核心设计

每个计算托盘(节点)包含 16 颗 LPU、2 颗阿尔特拉 FPGA、1 颗英特尔 Granite Rapids 主机 CPU 与 1 个 BlueField-4 前端模块(超大规模客户可替换为自定义网卡)。

LPU 部署方式:采用 “背对背” 安装,PCB 上表面与下表面各 8 个 LP30 模块,所有 LPU 互联通过 PCB 走线实现。这种设计可缩短 X、Y 维度的 PCB 走线长度,满足节点内全对全互联的高密度布线需求。

FPGA 的三大作用:

网卡功能:将 LPU 的 C2C 协议转换为以太网,连接 Spectrum-X 扩展网络,实现 LPU 与 GPU 的解码系统互联。

协议转换:将 LPU 的 C2C 协议转换为 PCIe,实现 LPU 与主机 CPU 的通信(LPU 无原生 PCIe PHY,无法直接连接 CPU)。

控制与内存扩展:通过背板与节点内其他 FPGA 互联,管理 LPU 的控制流与时序;每颗 FPGA 可提供高达 256GB 的额外系统 DRAM,若用户需完全由 LPX 承担解码流程,该内存池可用于 KV 缓存。

前端接口:8 个 OSFP 插槽用于跨机柜 C2C 互联;2 个 QSFP-DD 插槽连接 Spectrum 交换机,实现 LPU 与 GPU 的解耦解码系统互联。

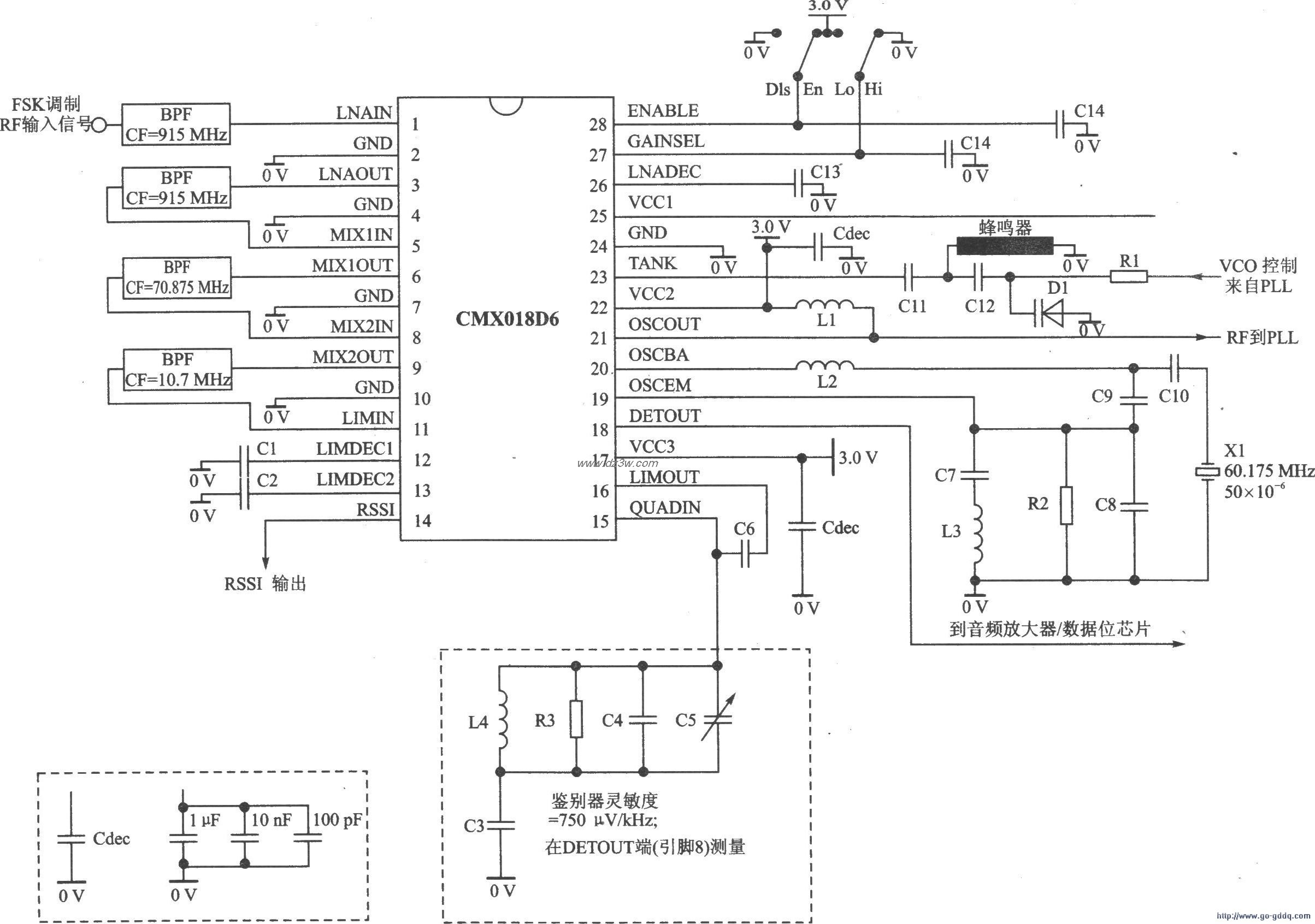

3. LPU 网络架构(分为扩展网络与外联网络)

(1)扩展网络(C2C 网络)

分为节点内、节点间 / 机柜内、机柜间三个层级,英伟达宣称单机柜扩展带宽达 640TB/s(计算逻辑:256 颗 LPU × 90 通道 × 112Gbps/8 × 2 方向 = 645TB/s,注:英伟达采用 112G 线速计算,而非 100G 有效数据率)。

节点内拓扑:16 颗 LPU 采用全对全互联,每颗 LPU 与其他 15 颗 LPU 通过 4×100G C2C 带宽连接(非 NVLink,为 Groq 原生扩展网络),所有连接通过 PCB 走线实现。每颗 LPU 还通过 1×100G 连接至 1 颗 FPGA,每颗 FPGA 通过 8×PCIe Gen5 连接至 CPU。

节点间 / 机柜内拓扑:每颗 LPU 与机柜内其他 15 个节点的对应 LPU 通过 2×100G 铜缆背板连接;每颗 FPGA 与其他节点的 FPGA 通过 25G/50G 链路连接(同样通过背板)。单个节点需 510 个通道(1020 个差分对)用于节点间互联。

机柜间拓扑:每颗 LPU 通过 4×100G 通道连接至 OSFP 插槽,支持跨 4 个机柜互联。推荐采用菊花链配置,节点 0 与其他 2 个节点 0 连接,两端通过 9 米 AEC 线缆或光模块连接形成环形网络。

(2)外联网络

通过 Spectrum-X 以太网,实现 LPU 与英伟达 GPU 的通信。

四、英伟达 CPO 路线图

英伟达在 2026 年 GTC 主题演讲中首次披露 CPO(共封装光学)路线图,黄仁勋在次日的财务分析师问答会上进一步补充说明。与行业预期不同,英伟达并未将 CPO 用于 Rubin Ultra Kyber 机柜的内部扩展,而是聚焦于构建更大规模的计算系统。

1. GTC 2026 披露的机柜级形态与 CPO 应用

系统 | Rubin 系列 | Feynman 系列 | ||||

NVL 规格 | NVL72 | NVL144 | NVL576 | NVL72 | NVL144 | NVL1152 |

形态 | Oberon | Kyber | 8 个 Oberon 机柜 | Oberon | Kyber | 8 个 Kyber 机柜 |

机柜内扩展 | 铜背板 | PCB 中板 + 飞线 | 铜背板 | 铜背板(推测) | PCB 中板 + 飞线(推测) | 铜或 CPO(未确定) |

机柜间扩展 | 无 | 无 | CPO(DR 光模块) | 无 | 无 | CPO(DR 或 DWDM) |

2. 各代产品 CPO 应用规划

Rubin 系列:

NVL72(Oberon):全铜扩展网络。

Rubin Ultra NVL72(Oberon)、NVL144(Kyber)、NVL288(2 个 Kyber 机柜互联):均采用全铜扩展网络。

Rubin Ultra NVL576(8 个 Oberon 机柜互联):机柜内铜扩展,机柜间采用两层全对全网络的 CPO 扩展(低批量测试用途)。

Feynman 系列:

NVL72(Oberon)、NVL144(Kyber):全铜扩展网络。

NVL1152(8 个 Kyber 机柜互联):机柜内铜扩展,机柜间 CPO 扩展(黄仁勋称 “全 CPO”,但机柜内是否仍用铜存在争议)。

3. 技术决策逻辑

英伟达的核心原则是 “能用电铜则不用光”:

当前 224Gbit/s 双向 SerDes 难以升级至 448Gbit/s 单向,带宽提升有限;

448G 高速 SerDes 在传输距离、功耗上面临巨大挑战,且 Feynman 的制造复杂度、成本与可靠性要求,决定了交换机仍需采用铜互联。

注:NVL1152 距量产尚有多年,路线图可能调整,当前基准假设为 “机柜内铜、机柜间 CPO”。

五、Oberon 与 Kyber 更新:更大规模扩展与网络升级

1. Kyber 机柜形态更新

Kyber 机柜首次作为原型机在 2025 年 GTC 展示,此次披露的量产版本有显著调整:

计算刀片密度提升:每个计算刀片含 4 颗 Rubin Ultra GPU 与 2 颗 Vera CPU;共 2 个罐式单元,每个单元 18 个计算刀片,整机柜 36 个计算刀片,合计 144 颗 GPU。(初代原型机每个计算刀片含 2 颗 GPU 与 2 颗 Vera CPU,共 4 个罐式单元)。

交换刀片高度翻倍:每个交换刀片含 6 颗 NVLink 7 交换机,整机柜 12 个交换刀片,合计 72 颗 NVLink 7 交换机。

互联方式:GPU 通过 2 块 PCB 中板(每罐 1 块)与交换刀片全对全互联;交换机与中板通过铜质飞线连接(距离过远,无法通过 PCB 走线)。

2. Rubin Ultra NVL144 核心参数

单 GPU 扩展带宽:14.4Tbit/s 单向(采用 80DP 连接器,72 个 DP 通道 × 200Gbit/s 双向通道)。

交换机规格:每颗 NVLink 7 交换机单向聚合带宽 28.8Tbit/s,含 144 个 200G 双向通道;每个交换刀片通过 144 个 DP 连接器(144 × 200G 双向通道)与中板连接。

3. 更大规模扩展方案

Rubin Ultra NVL288:供应链透露的概念方案,由两个 NVL144 Kyber 机柜通过机柜间铜背板互联。面临的挑战:当前 NVLink 7 交换机最大端口基数仅 144 个(200G 端口),若实现 288 颗 GPU 全对全互联,需更高基数交换机,或采用蜻蜓网络拓扑并接受一定程度的超订阅。

Rubin Ultra NVL576:8 个低密 Oberon 机柜互联,机柜间需光互联(CPO 概率高于可插拔光模块),形成两层胖树架构。当前 Blackwell NVL576 原型机 “Polyphe” 采用可插拔光模块,但 Rubin Ultra NVL576 预计先以低批量测试形式推出,待 Feynman NVL1152 量产时,CPO 才会大规模应用。

六、Feynman 架构前瞻

Feynman 虽未披露过多细节,但从大会预览可知,其将集成三大核心技术创新:混合键合 / 系统级芯片互联(SoIC)、A16、CPO 与定制 HBM,是极具突破性的平台。核心悬念在于 CPO 的应用范围 —— 机柜内互联将沿用铜还是转向光,后续将在付费内容中披露可能的配置方案。

七、Vera ETL256:超高密度 CPU 机柜

人工智能工作负载对数据处理、预处理与调度的需求日益增长,强化学习进一步提升 CPU 需求(CPU 需并行运行模拟、执行代码、验证输出)。由于 GPU 性能增长速度远超 CPU,需更大规模的 CPU 集群才能充分发挥 GPU 算力,CPU 已成为日益突出的瓶颈。

Vera ETL256 机柜专为解决这一问题设计,通过液冷实现超高密度部署:单机柜集成 256 颗 CPU,设计理念与 NVL 机柜一致 —— 通过极致密集的计算布局,让铜互联可覆盖机柜内所有节点,省去骨干网的光模块,铜互联的成本节省远超额外的冷却开销。

1. 机柜结构

32 个计算托盘(上下各 16 个),对称分布在中间 4 个 1U MGX ETL 交换机托盘(基于 Spectrum-6)两侧,最小化计算托盘与骨干网的线缆长度差异,确保所有连接在铜互联范围内。

交换机托盘的后置端口连接铜骨干网,用于机柜内通信;32 个前置 OSFP 插槽提供光互联,连接其余 POD 节点。

机柜内采用 Spectrum-X 多平面拓扑,将 200Gb/s 通道分布在 4 个交换机上,实现单层网络的全对全互联。每个计算托盘含 8 颗 Vera CPU,整机柜 256 颗 CPU 通过以太网实现扁平互联。

1. CMX(推理上下文内存存储平台)

前身为 ICMS(推理上下文内存存储),是英伟达推出的 “G3.5 层” 存储解决方案,位于 G3 层(本地 SSD)与 G4 层(共享存储)之间,专为解决长上下文与智能体式工作负载中 KV 缓存快速扩张的瓶颈。

KV 缓存存储层级挑战

存储层级 | 介质 | 访问延迟 | 应用场景 | 核心特点 |

G1 | GPU HBM | 纳秒级 | 活跃 KV 缓存(生成中) | 访问最快,每瓦性能、性价比最优 |

G2 | 系统 DRAM | 纳秒级 | 暂存 / 溢出 KV 缓存 | 延迟递增,每 token 开销上升 |

G3 | 本地 SSD / 机柜本地存储 | 微秒级 | 短期复用的热 KV 缓存 | 延迟较高 |

G4 | 共享对象 / 文件存储 | 毫秒级 | 冷 KV 缓存或共享 KV 上下文 | 延迟最高,推理瓶颈,限制扩展,效率最低 |

CMX 的本质是通过 BlueField 网卡连接存储服务器与计算服务器(替代原有的 Connect-X 网卡),为 KV 缓存提供额外的卸载层级,缓解本地存储容量不足与共享存储延迟过高的矛盾。

2. STX:参考存储机柜架构

STX 是基于英伟达 BlueField-4 的存储解决方案参考架构,用于补充 VR 计算机柜,明确规定了特定集群所需的硬盘、Vera CPU、BlueField-4 数据处理单元(DPU)、CX-9 网卡与 Spectrum-X 交换机数量。

核心配置

每个 STX 盒含 2 个 BlueField-4 单元,每个单元含 1 颗 Vera CPU、2 颗 CX-9 网卡、2 个 SOCAMM 模块;整机柜 16 个 STX 盒,合计 32 颗 Vera CPU、64 颗 CX-9 网卡、64 个 SOCAMM 模块。

支持厂商包括 AIC、Cloudian、DDN、戴尔科技、爱惠浦、日立 Vantara、HPE、IBM、MinIO、NetApp、Nutanix、超微、广达云、VAST Data、WEKA 等主流存储厂商。

3. 战略意义

BlueField-4、CMX 与 STX 共同构成英伟达存储层集群标准化的核心布局。在掌控计算与网络层后,英伟达正逐步向存储、软件与基础设施运营层扩张。

评论