卷积编码及Viterbi 解码的FPGA 实现及应用

5 卷积码译码--Viterbi 译码的FPGA 实现

Viterbi算法的基本实现方法如下:在不同时刻,按照最大似然准则将网格图中所有的路径进行比较,保留一条具有最大似然值的路径(幸存路径),同时舍弃其他路径。每个时刻进行相同的操作,对每接收到的一段数据进行计算、比较并保存幸存路径,最后留下的路径就是所要求得的译码值。

对于卷积码(2,1,7),其编码的状态数为26,所以在译码时,译码器最多需要保留26条幸存路径,和它所对应的路径度量值。由于是(2,1,7)编码每个节点将引出两条支路,但通过比较似然函数的累加值后,可以丢弃一半的路径,使得留存下来的路径总数保持不变。这样在具体实现时可以开辟固定大小的存储区,有利于硬件资源的估计。

在工程实现中采用迭代的方法,在每个时刻,对进入每个状态的所有路径的量度值进行比较,同时把具有最大量度值的路径存储下来。具体步骤如下:

(1)初始化,从时刻t = n 起,计算每个状态的路径和路径度量,并存储。

(2)在t + 1 时刻,接收新的一组数据,将当前的路径度量与前一时刻的度量相加,求得并保存最大度量并保存幸存路径,删除其余路径(3)当t L + n( L 为反馈深度)时重复步骤(2),否则结束输出结果。

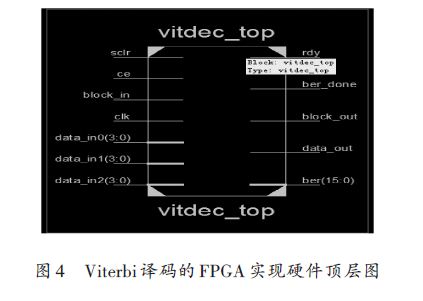

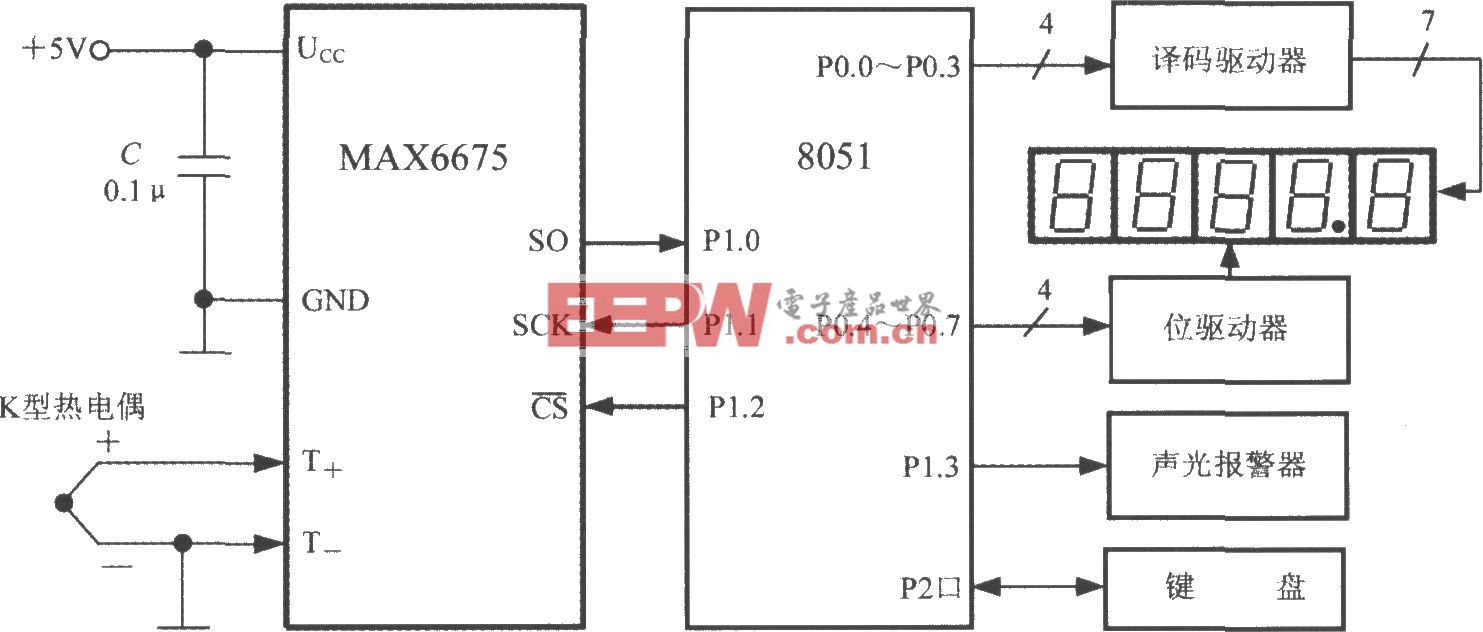

由于软判决可以对信道噪声进行更好的估计,因此它比硬判决有着更好的译码性能。因此,本文Viterbi译码器采用软判决算法,同时对信号采用线性(均匀)八电平量化。其FPGA的实现图如图4所示。

6 系统应用

在一般的通信系统中卷积编码和Viterbi译码可以是连续的,但在实际系统的应用中由于系统采用PCM分帧的模式传送,因此卷积码编码和Viterbi译码也相应改成按帧传送模式。由于卷积码的编码是数据前后相关的一种编码模式,在按帧发送后设编码和解码的初始状态均为0,如(2,1,7)编码举例,从编码的原理图2中可以清楚的看到,在相同的信道状态和传输数据一定的条件下,每一帧都将影响最后6 b 数据解码的正确性。

为此可以有两种解决方式:

(1)为每帧数据添加固定的6 b 数据,这种做法增加了系统的数据冗余;

(2)编码端不做任何处理,影响系统的误码率。

考虑到系统性能,由于系统传输能力还有剩余因此采用第一种处理方法。同时加入6 b 数据全部为0,这样不仅解决了数据误码率的问题同时保持了解码初始状态的一致性,使解码能更好的同步,有效地提高解码的正确性。

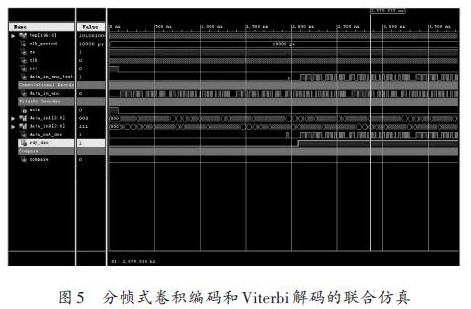

分帧式卷积编码及Viterbi 解码的FPGA 实现的联合仿真如图5所示。

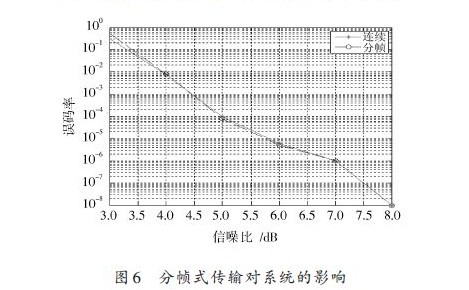

分帧式传输对系统的影响如图6所示。

7 结论

在实际通信系统中,通过测量比较,分帧式编解码和连续编解码相比,在信道传输中对系统影响不大,在某些情况下分帧式编解码甚至会优于连续编解码。

评论