精密ADC 用滤波器设计的 实际挑战和考虑

电阻的非线性有两个来源:电压系数和功率系数。根据具体应 用,高性能信号链可能需要使用由特定技术制造的电阻,如薄 膜或金属电阻。如果选择不当,输入滤波电容可能会造成显著 失真。如果成本预算允许,聚苯乙烯和NP0/C0G 陶瓷电容是 很好的备选元件,可以改善THD。

除放大器噪声外,电阻和电容也会有电子噪声,后者是由处于 均衡态的电导体内部的电荷载子的热扰动产生的。RC 电路的 热噪声有一个简单的表达式,电阻R 是满足滤波要求所需要 的,同时R 越高,相应的热噪声也越大。RC 电路的噪声带宽 为1/(4RC)。

利用下面两个公式可估算电阻和小电容的均方根热噪声。

kB (玻尔兹曼常数) = 1.38065 × 10–23m2kgs–2K–1

T 为温度 (K)

f 为砖墙滤波器近似带宽

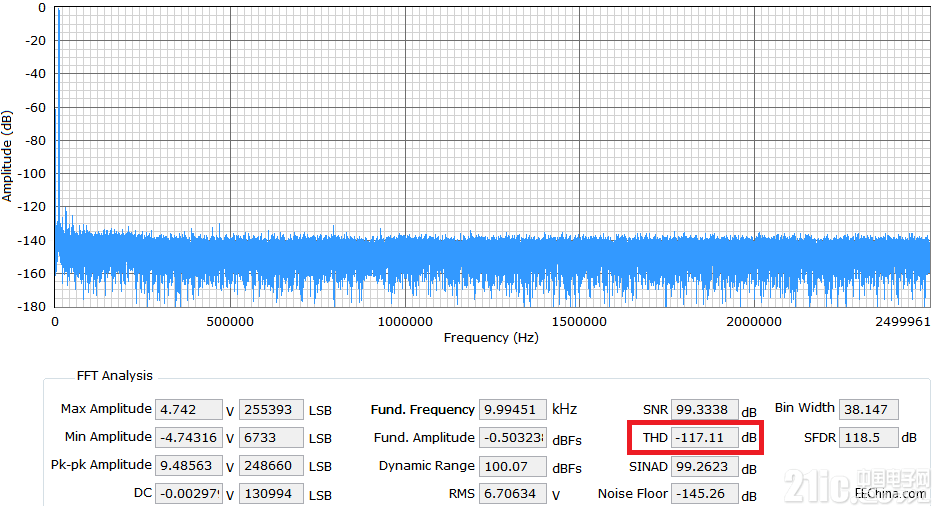

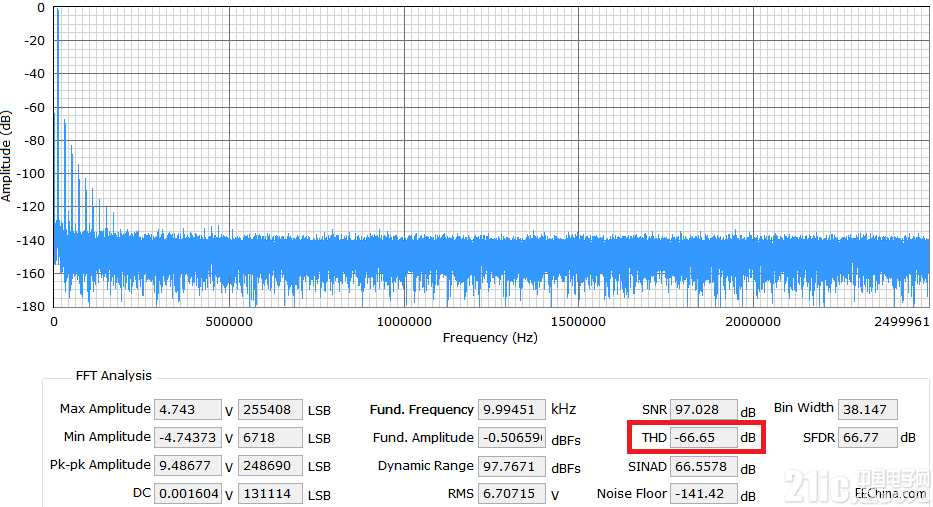

图6 显示在EVAL-AD7960FMCZ 评估板上,NP0 电容和X7R 电容对THD 性能的影响:(a) 显示一个10 kHz 正弦波信号音 的频谱,C76 和C77 为1 nF 0603 NP0 电容,而 (b) 显示使用 1 nF 0603 X7R 电容时的频谱。

(a) 0603 1nF NP0 电容

(b) 0603 1nF X7R 电容

图6.在EVAL-AD7960FMCZ 评估板上NP0 和X7R 电容对THD 的影响

了解前面的设计考虑之后,便可利用ADI 公司的模拟滤波器向导设计有源模拟滤波器。它会根据应用要求计算电容和电阻值,并选择合适的放大器。

数字滤波器考虑

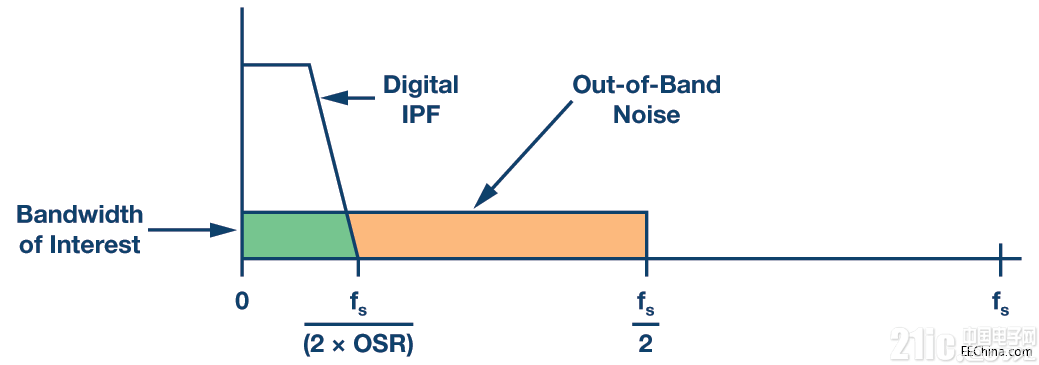

SAR 型和Σ-Δ 型ADC 正在稳步实现更高的采样速率和输入带 宽。以两倍奈奎斯特速率对一个信号过采样,会将ADC 量化 噪声能量均匀扩散到两倍频段中。这样便很容易设计数字滤波 器来限制数字化信号的频带,然后通过抽取来提供所需的最终 采样速率。这种技术可降低带内量化误差并提高ADC SNR。 它还能放宽滤波器滚降要求,从而减轻抗混叠滤波器的压力。 过采样降低了对滤波器的要求,但需要更高采样速率ADC 和 更快的数字处理。

1. 对ADC 使用过采样速率所取得的实际SNR 改善

利用过采样和抽取滤波器所取得的SNR 改善,可从N 位ADC 的 理论SNR 求得:SNR = 6.02 × N + 1.76 dB + 10 × log10[OSR], OSR = fs/(2 × BW)。注意:此公式仅适用于只存在量化噪声的 理想ADC。

图7.奈奎斯特转换器过采样

还有很多其他因素会将噪声引入ADC 转换代码中。例如:信 号源和信号链器件的噪声,芯片热噪声,散粒噪声,电源噪声, 基准电压噪声,数字馈通噪声,以及采样时钟抖动引起的相位 噪声。这种噪声可能会均匀分布在信号频段中,表现为闪烁噪 声。因此,实际实现的ADC SNR 改善幅度一般低于用公式计 算出的值。

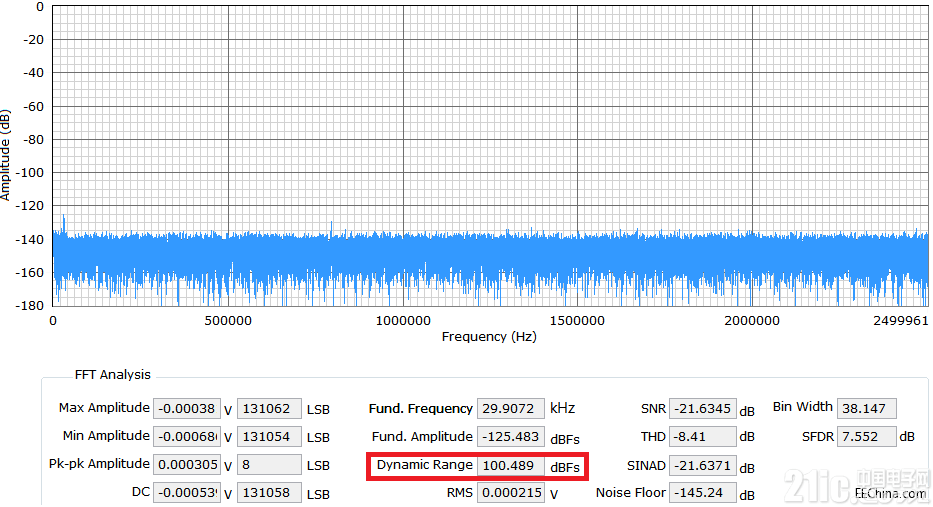

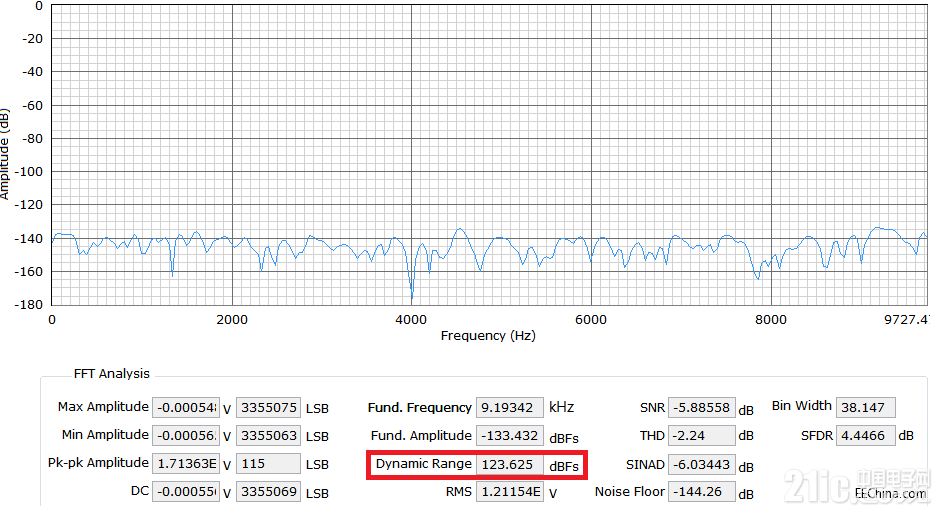

2. EVAL-AD7960FMCZ 评估板上利用过采样实现的动态改善

在应用笔记AN-1279 中,256×过采样下18 位AD7960 ADC 的 实测动态范围为123 dB。这是用于高性能数据采集信号链,如 光谱分析、磁共振成像 (MRI)、气相色谱分析、振动、石油/ 天然气勘探和地震系统等。

如图8 所示,与理论SNR 改善幅度计算相比,测得的过采样 动态范围低1 dB 至2 dB。原因是来自信号链器件的低频噪声 限制了总体动态范围性能。

(a) 无OSR 的动态范围

(b) OSR = 256 的动态范围

图8.OSR 256 时的动态范围改善

3. 充分利用SAR 型和Σ-Δ 型ADC 中的集成数字滤波器

数字滤波器通常位于FPGA、DSP 或处理器中。为了减少系统 设计工作,ADI 公司提供了一些集成后置数字滤波器的精密 ADC。例如,AD7606 集成了一个一阶后置数字sinc 滤波器用 于过采样。它很容易配置,只需上拉或下拉OS 引脚。Σ-Δ 型 ADC AD7175-x 不仅有传统sinc3 滤波器,还有sinc5 + sinc1 和增强型50 Hz/60 Hz 抑制滤波器。AD7124-x 提供快速建立模 式(sinc4 + sinc1 或sinc3 + sinc1 滤波器)功能。

4.多路复用采样ADC 的延迟取舍

延迟是数字滤波器的一个缺点,它取决于数字滤波器阶数和主 时钟速率。对于实时应用和环路响应时间,应当限制延迟。数 据手册所列的输出数据速率是指在单一通道上执行连续转换 时转换结果有效的速率。当用户切换到另一通道时,建立Σ-Δ 调制器和数字滤波器还额外需要些时间。与这些转换器相关的 建立时间是指通道变更之后输出数据反映输入电压所需的时 间。通道变更之后,为精确反映模拟输入,必须清除数字滤波 器中与前一模拟输入相关的全部数据。

以前,Σ-Δ 型ADC 的通道切换速度比数据输出速率要小得多。 因此,在多路复用数据采集系统等切换应用中,必须明白:获 得转换结果的速率要比对单一通道连续采样时可达到的转换 速率低好几倍。

ADI 公司的某些新型Σ-Δ ADC(如AD7175-x)内置优化的数字 滤波器,可减少通道切换时的建立时间。AD7175-x 的sinc5 + sinc1 滤波器主要用于多路复用应用,在10 kSPS 和更低的输出 数据速率时,可实现单周期建立。

5.数字滤波器通过抽取避免混叠

很多文章都讨论过,过采样频率越高,模拟滤波器设计就越容 易。当采样速率高于满足奈奎斯特准则所需的速率时,便可使 用较简单的模拟滤波器来避免受到极高频率所产生的混叠影 响。很难设计一个能够衰减所需频段而不失真的模拟滤波器, 但很容易设计一个利用过采样抑制较高频率的模拟滤波器。这 样便很容易设计数字滤波器来限制转换信号的频带,然后通过 抽取来提供所需的最终采样速率,但又不会丧失所需信息。

实施抽取之前,需要确保这种重新采样不会引入新的混叠问 题。抽取之后,确保输入信号符合奈奎斯特关于采样速率的 理论。

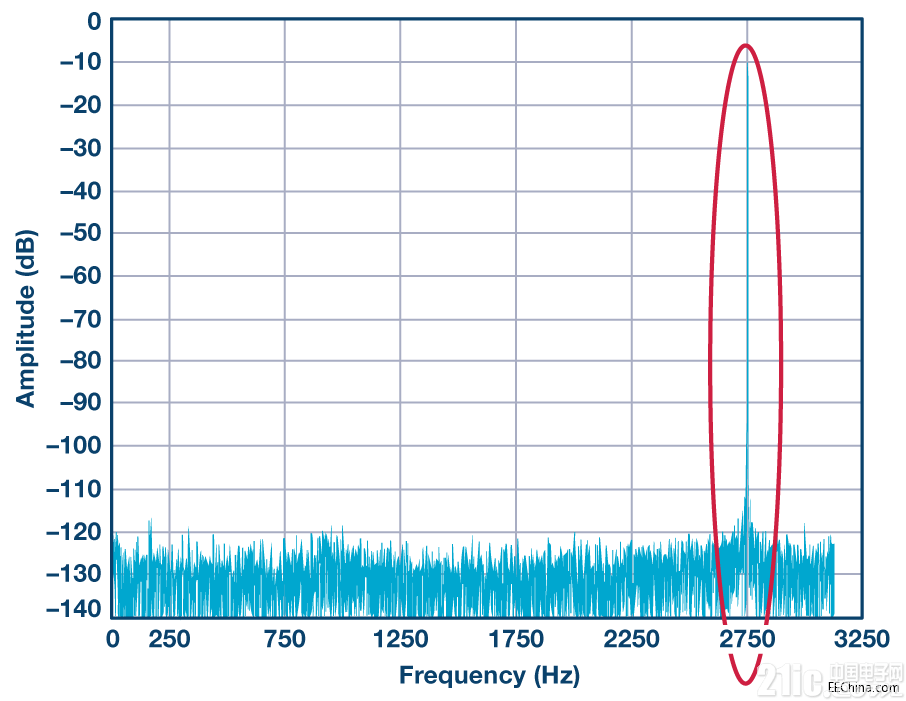

EVAL-AD7606/EVAL-AD7607/EVAL-AD7608EDZ 评估板可以每 通道200 kSPS 的速率运行。在下面的测试中,配置其采样速率为 6.25 kSPS,过采样比为32。然后,将一个3.5 kHz –6 dBFS 正弦 波施加于AD7606。图9 显示2.75 kHz (6.25 kHz – 3.5 kHz) 处有 一个–10 dBFS 混叠镜像。因此,若ADC 之前没有合格的抗混叠 模拟滤波器,当使用过采样时,数字滤波器就可能会因为抽取而 引起混叠镜像。应使用模拟抗混叠滤波器来消除这种叠加于模拟 信号上的噪声尖峰。

图9.OSR 抽取采样率小于奈奎斯特频率时的混叠

结论

本文讨论的挑战和考虑可帮助设计人员设计出实用的滤波器 以实现精密采集系统的目标。模拟滤波器必须在不违反系统误 差预算的条件下与SAR 型或Σ-Δ 型ADC 的非理想输入结构接 口,数字滤波器不应在处理器端引起误差。这不是简单的任务, 必须在系统规格、响应时间、成本、设计工作量和资源等方面 做出权衡。

评论