使用ADSP-CM408F ADC控制器的电机控制反馈采样时序

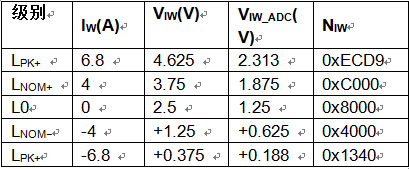

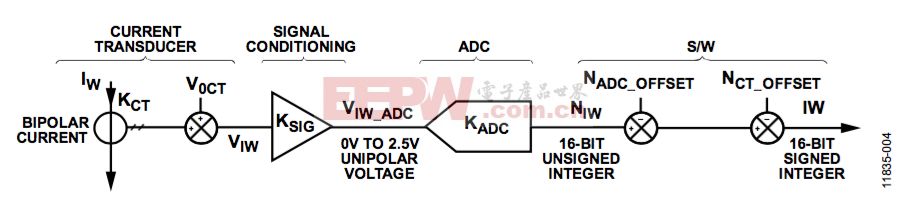

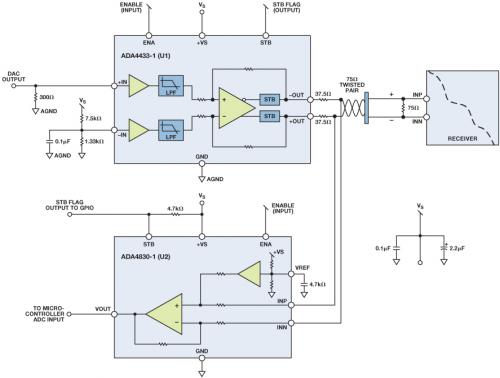

该情况的一个示例如图4所示。该图显示了典型电流波形和相关的各种零电平、峰值电平以及标称电平,图4显示的电流电平将转换为通过信号测量系统传播(如图5所示)的比例量(参见表1)。

本文引用地址:https://www.eepw.com.cn/article/201607/293857.htm

图4. 电流反馈信号幅度

表1. 电流反馈信号幅度

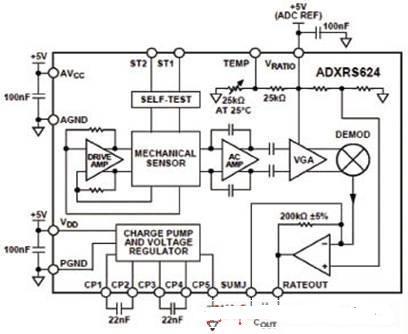

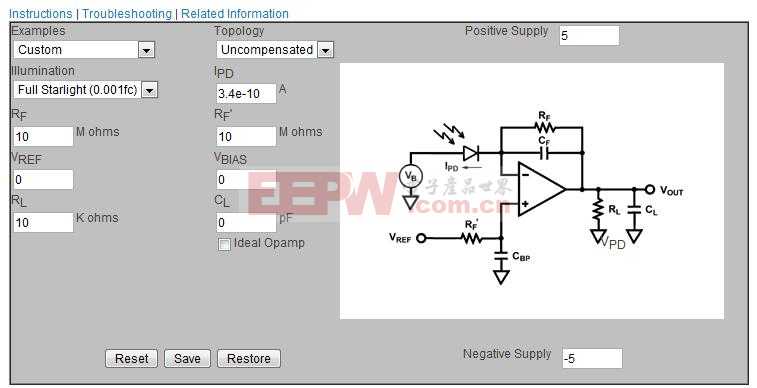

本示例采用连接LEM®,的CAS 6-NP霍尔效应传感器,其初级匝数为3,具有0 V至5 V输出,后接增益为0.5的信号调理电路。

图5. 电流反馈路径的调整关系

ADC操作时序

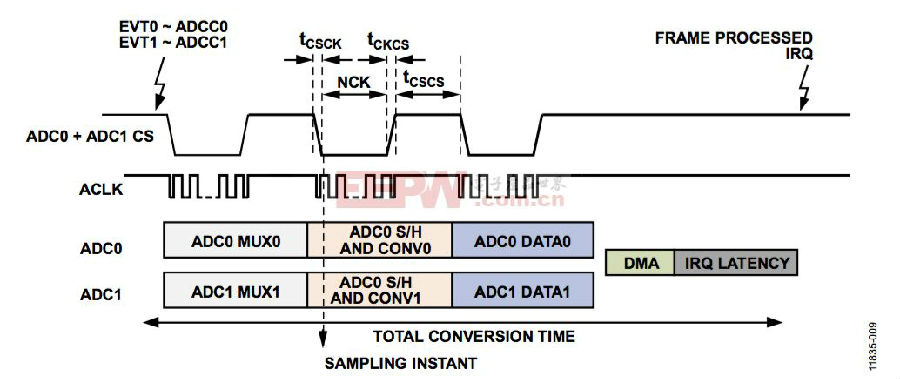

ADCC控制器触发采样事件后,ADC操作本身具有一个转换时间延迟。图9显示单次ADC事件与每个ADC接口相关联,且使能两次事件同步采样的情况。

有三个独立的转换周期与ADC操作有关。

1. 写入8位控制字,选择ADC读取通道(ADCC_EVTCTL.CTLWD)。

2. 置位转换脉冲,使能ADC采样和转换。

3. 让16位ADC数据回流至ADCC。

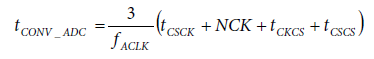

ADCC提供这3个事件相位的片选和选通时钟信号。ADCC与ADC的接口为串行接口,采用双通道位操作。因此,每个CS脉冲期间提供的最小时钟周期数(ADCC时序控制寄存器的NCK段)为8。其他重要的设置有:ADC时钟频率、转换周期片选信号之间的最小延迟(tCSCS)(ACLK周期内),以及CS边沿和ACLK边沿之间的最小延迟(tCSCK和tCKCS)。因此,单个同步采样信号对的ADC转换周期时间tCONV_ADC可表示为:

其中,fACLK表示ADCC时钟频率。

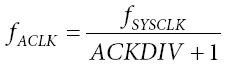

ADCC时钟由处理器系统时钟(fSYSCLK)通过ACKDIV分频(在时序控制寄存器ADCC_TCA中)在内部产生,计算如下:

其结果是系统时钟来源于处理器内核时钟(fCORECLK)。当fCORECLK为fSYSCLK的整数倍时,获得最佳系统性能。完成ADC转换后,额外延迟是因为ADC数据通过DMA传输至数据存储器,并最终由中断请求服务将数据帧准备就绪,供主应用程序使用。因此,在应用中,从触发(例如,PWM SYNC脉冲)到数据可用的总时间为:

tCONV_TOTAL = tCONV_ADC + tDMA + tIRQ

其中:

tDMA是DMA传输的平均时间。

tIRQ是中断请求服务的平均时间。

图9. 单次事件同步采样的转换时间

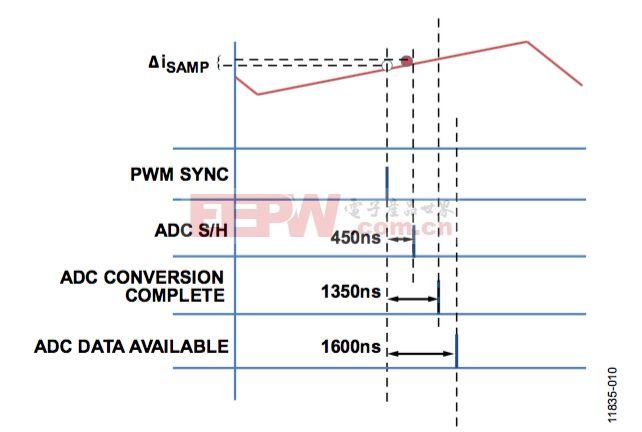

典型时序设置见表2。表中还列出了对时序的一些约束条件。获得正确ADC性能的绝对约束条件是,允许的ADC采样和转换周期(tCONV_ADC/3)必须至少为380 ns。单个同步采样事件的时序结果如图10所示,该结果与电机绕组电流的采样有关(注意,该图为了突出示例而略为夸大)。

图10. 采样延迟时间

采用这些设置时,在所需的电流波形采样点与实际采样点之间存在450 ns失调。该值等于一个片选脉宽(200 ns + 25 ns + 0 ns)加两次片选之间的脉宽(225 ns)。 该结果造成平均电机绕组电流和实际采样电流之间的ΔiSAMP产生差异,在时序调度中需加以考虑,虽然在1 kHz的典型电流控制环路带宽环境中,这表示不超过0.2°的相移。此外,对于10 kHz的典型PWM频率,ADC数据从产生PWM SYNC脉冲(表2中的设置)起,在不足2%的可用PWM周期时间内可供应用程序使用。如果在事件发生时ADC处于空闲状态,则4至5个SYSCLK周期的额外延迟将存在于事件激活的时刻与ADC开始工作的时刻之间。

图11. 采样时刻调整的实现

表2. 典型ADC设置的时序设定

评论