数字电子系统的EDA设计方法研究

2.1 控制模块的设计

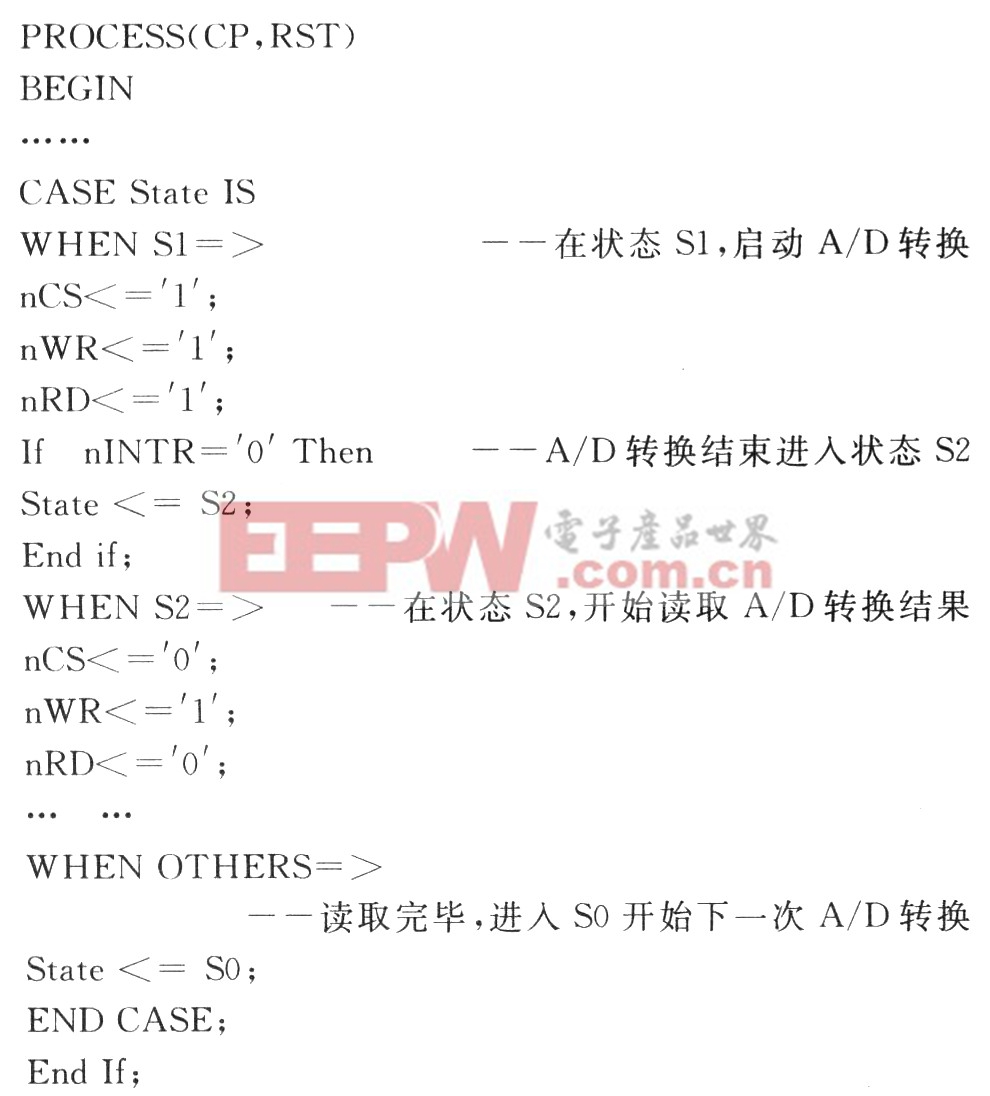

该模块的任务是,控制ADC0804的工作时序,可分为S0~S3四个连续的步骤或状态。任务分别是:使ADC0804准备转换(状态S0)、转换(状态S1)、CPLD准备读取转换结果(状态S2)、读取转换结果(状态S3)。各状态由CPLD输出脚CS、WR、RD的不同电平组合确定,主要的VHDL语句为:本文引用地址:https://www.eepw.com.cn/article/191900.htm

2.2 计算模块

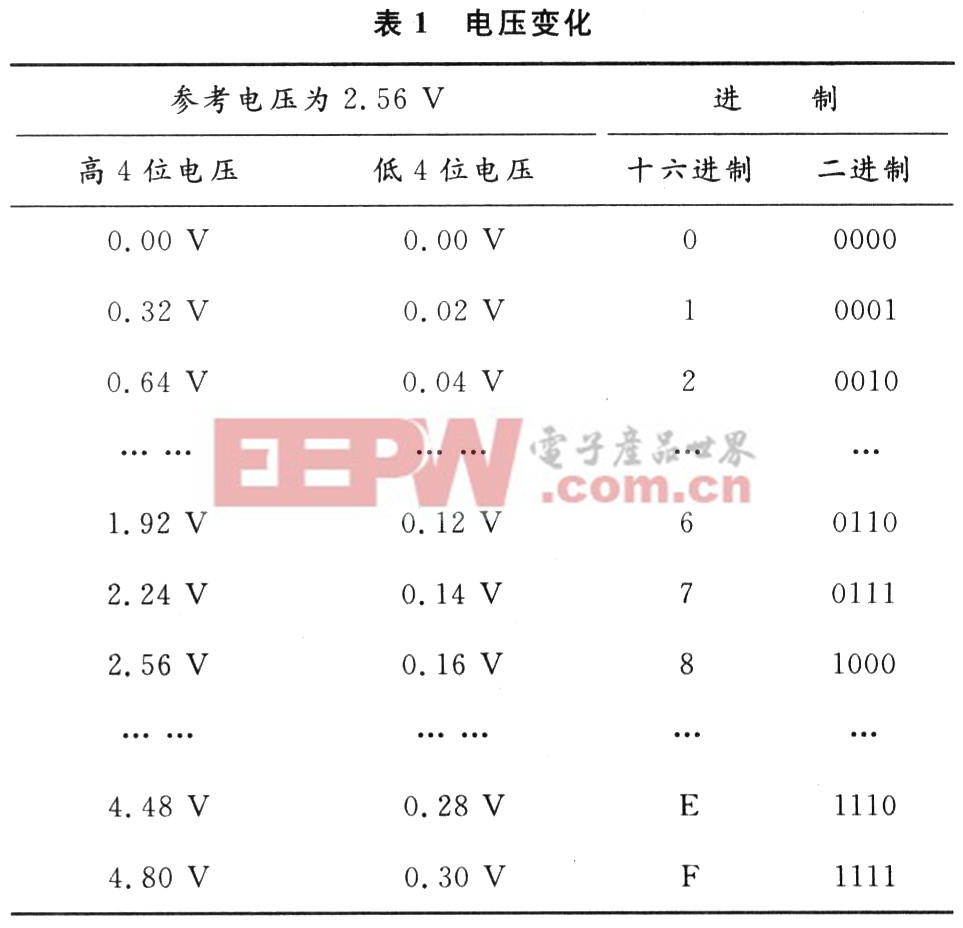

该模块将A/D转换结果分为高低4位,查表依次得到其BCD码后再进行计算,计算结果与A/D转换器的位宽和参考电压Vref均有关。本文选用8位转换器ADC0804,参考电压为5.12 V,故能输出从0~5.12 V按照0.02 V步进变化的256(28)个离散值。如表1所示。

电压离散值可用8位二进制(或2位十六进制数)表示,表1中列出了输出数字电压高4位及低4位可能出现的16个值。如果CPLD从ADC20804接收到信号01101000B(即68H),对照表1高4位0110B是1.92 V,而低4位1000B是0.16 V,则最后的电压输出结果是1.92+0.16=2.08 V。

本文要求精确到两位小数0.01 V,故将输出电压表示成12位的BCD码形式。如上述的1.92 V是(000110010010)BCD,0.16 V是(000000010110)BCD,相加结果2.08 V是(001000001000)BCD。同理,若CPLD转换数据01110000B(即70H),则计算结果2.24 V是(001000100100)BCD。因此计算模块的设计主要包括一个12位的加法器及与之对应的存储器。

评论