采用FPGA实现发电机组频率测量计的设计

3 频率测量计的设计

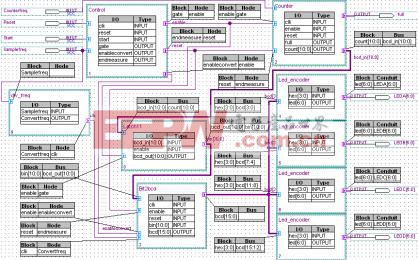

本次设计采用Verilog HDL语言,运用自顶向下的设计理念。将系统按功能按层次化分,首先定义顶层功能模块,并在顶层功能模块内部的连接关系和对外的接口关系进行了描述, 而功能块的逻辑功能和具体实现形式则由下一层模块来描述。整个设计分两步:第一步利用Quartus Ⅱ5.0图形块输入方式设计顶层模块,顶层图形块如图2所示;第二步在顶层模块中为每个图形块生成硬件描述语言(Verilog HDL),然后在生成的Verilog HDL设计文件中,对低层功能模块的功能进行描述设计。

图2 顶层图形块

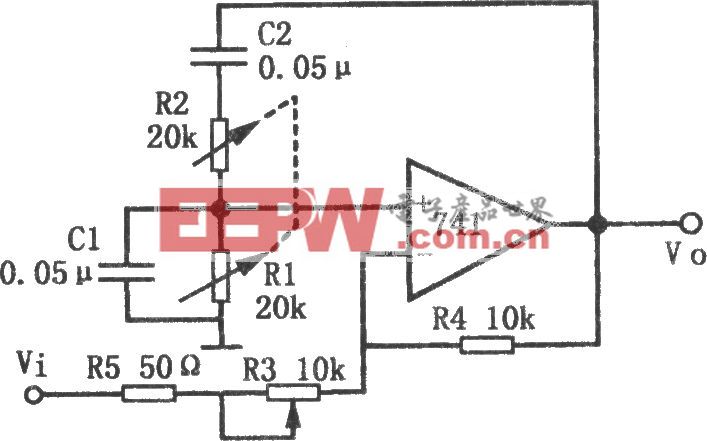

3.1 测频控制模块设计

这是三输入三输出模块,测频控制模块波形仿真如图3所示,如用Verilog HDL描述为:

module Control (clk,reset,start,enableconvert,gate,endmeasure);

input reset,start,clk;

output enableconvert,gate,endmeasure;

reg enableconvert,gate,endmeasure;

always @ (posedge clk or posedge reset)

begin

if (reset)

begin

endmeasure = 1'b1 ;

enableconvert =1'b0 ;

gate = 1'b0 ;

end

else

begin

endmeasure = 1'b0 ;

if (start)

begin

gate = ~gate ;

enableconvert = gate ;

end

end

end

endmodule

图3 测频控制器波形仿真时序图

评论