基于AVR和CPLD的高速数据采集系统

2.2 控制Flash存储程序设计

4个Flash存储器的流水线工作原理如图2所示,对单独的每一片Flash来说每一次存储都是在上一次存储过程中加载完成后进行,而对于由4片Flash存储器组成的整个系统,它一直在加载存储数据,这样可以保证存储速度大于采集速度,从而保证存储过程中不会因单片Flash存储速度慢而造成丢失数据。实现Flash存储的主要程序:

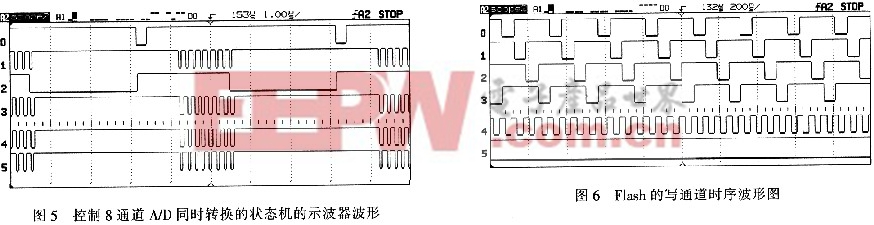

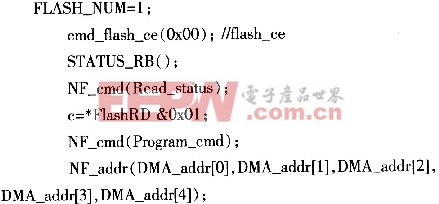

在数据加载期间本系统应采用DMA传输控制方式,即:每当FIF0的半满标志信号HF产生一次有效电平时,ATmegal62就启动一次中断,在中断程序中,ATmegal62将产生NAND Flash命令和有效地址,以及启动DMA控制器。一旦DMA控制器启动,ATmegal62就将转入后台进行有效地址的运算等,从而参与数据传输过程,整个数据从FIFO到Flash存储器的传输过程是由CPLD内部编写的DMA控制器控制完成。启动一次DMA控制器传输一页2048个字节的数据,一次中断完成16 K字节的传输。其示波器时序如图6所示:第0,1,2,3通道是FIF0的读数据时序波形,第4通道是Flash的写通道时序波形。

3 结论

通过使用AVR和CPLD编程,设计实现了一种成本低且可实现10 Mb/s以上并行采集数据率的高速数据采集存储系统。在分析MAXl308特性及转换时序的基础上,设计完成了A/D转换器及其外围电路,并通过调试可知时序稳定。通过VHDL语言实现了采集模块、控制与存储模块和Flash存储功能。在完成硬件连接后调试,试验结果显示,该设计能够实现低成本高速采集,多路同时采集速度大于10 Mb/s采集系统,具有一定的实用价值。

评论