基于AVR和CPLD的高速数据采集系统

2.1 控制A/D转换程序设计

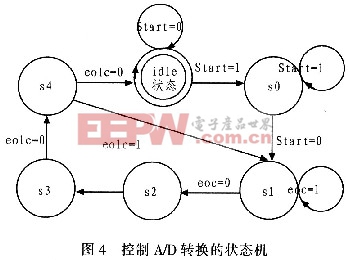

根据控制存储的要求,首先要设计控制A/D转换的状态机,用来确定A/D转换的状态,根据MAXl308工作时序特点而设计的控制A/D转换的状态机转换图如图4所示。实现控制A/D转换的状态机部分主要VHDL程序源代码如下:

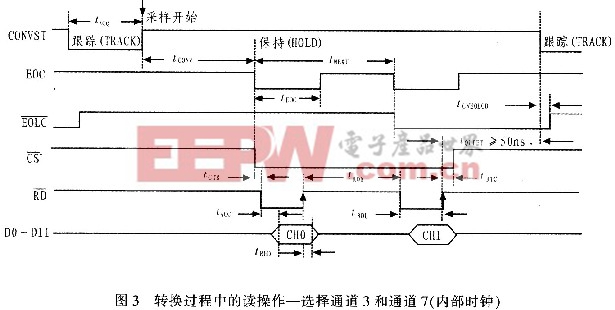

将程序下载至CPLD中运行调试,经过对电路的调试和测量,控制8通道A/D同时转换的状态机产生的示波器时序波形如图5所示,其中,0、1、2、3、4分别对应的是图3中的CONVST、EOC、EOLC、CS、RD,而第5通道是对FIF0的写信号。从示波器显示的波形图可以看出产生的8个连续的脉冲对应位置完全满足图3所要求的时序要求,也就是说在控制器同时控制8路信号的采集时不会出现时序混乱的情况。由此可知,采用本系统中设计的采集程序可以实现同时采集的要求,并且根据采集的脉冲宽度分析可知该系统能满足采集速度为10 Mb/s的设计要求。

评论