基于CPLD/FPGA的USB读写控制器

2 CPLD中的读写控制电路

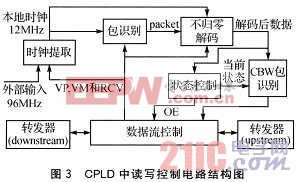

CPLD中的读写控制电路包括时钟提取、包识别、不归零解码、状态控制、CBW包识别和数据流控制等模块,如图3所示。时钟提取部分见参考文献,包识别和不归零解码部分见参考文献。下面详细介绍状态控制、CBW包识别和数据流控制3个模块。本文引用地址:https://www.eepw.com.cn/article/191139.htm

2.1 状态控制模块

因为IJSB总线是半双工的,所以CPLD要控制总线数据的方向,即通过OE信号来控制TUSB1106是接收总线数据还是驱动总线。总线上所有的传输事务都始于令牌包。令牌包由主机发送,指明本次事务处理过程的含义,包括数据的传输方向、设备的地址及端点号等信息。

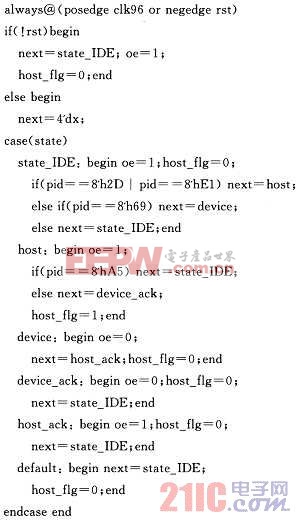

在本模块中,通过对PID的检测可得到每个包的种类,控制状态机在初始状态、主机发送数据、设备发送数据、主机发送握手包和设备发送握手包等几个状态间跳转,从而控制其他模块的状态。下面为状态机的部分代码:

评论