基于CPLD的系统硬件看门狗设计

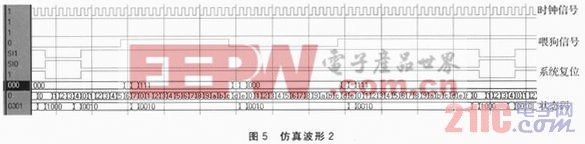

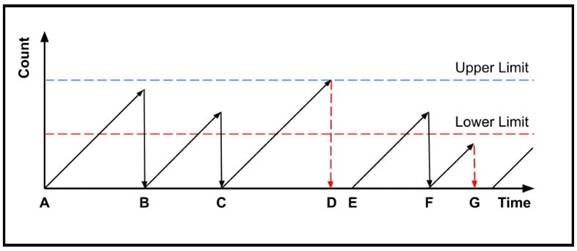

仿真波形2如图5所示。由仿真波形可看出,在EN高电平时,不会输出喂狗信号,使能信号测试通过,喂狗信号存EN使能时如不能存限定时间内喂狗,则输出系统复位信号。由仿真波形看出功能得到实现。

3.2 硬件平台验证

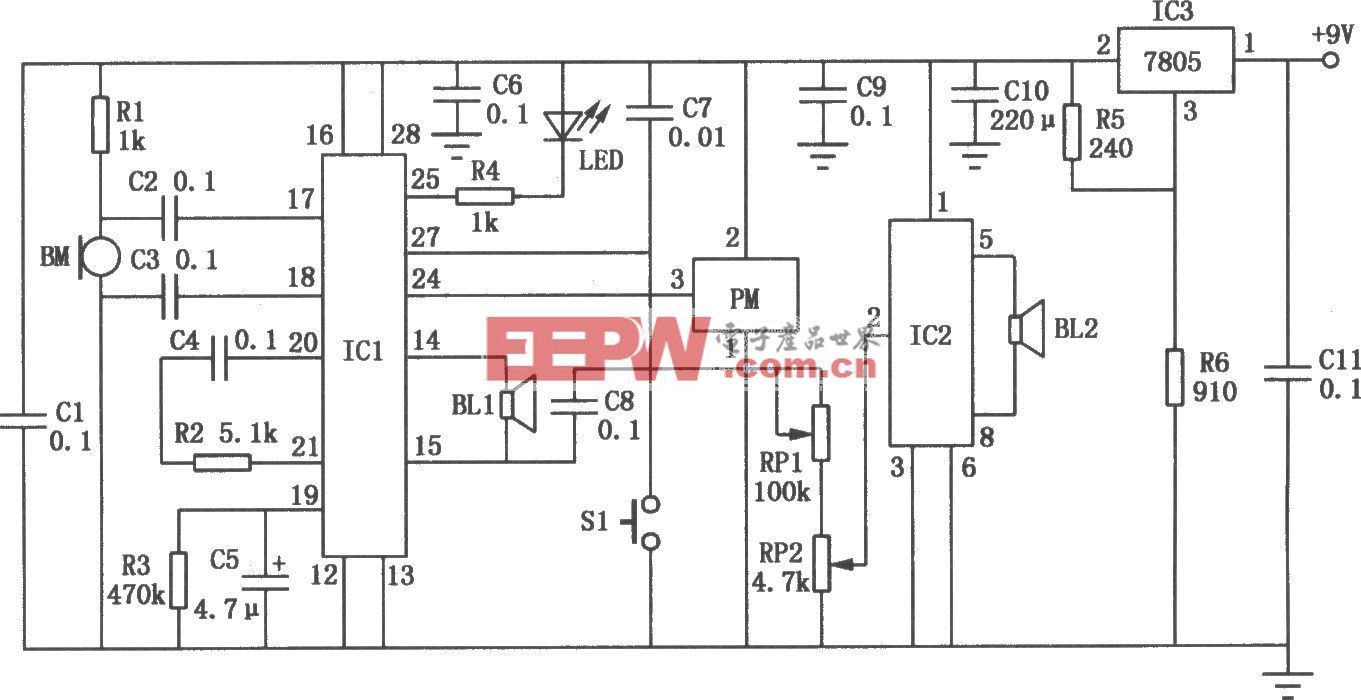

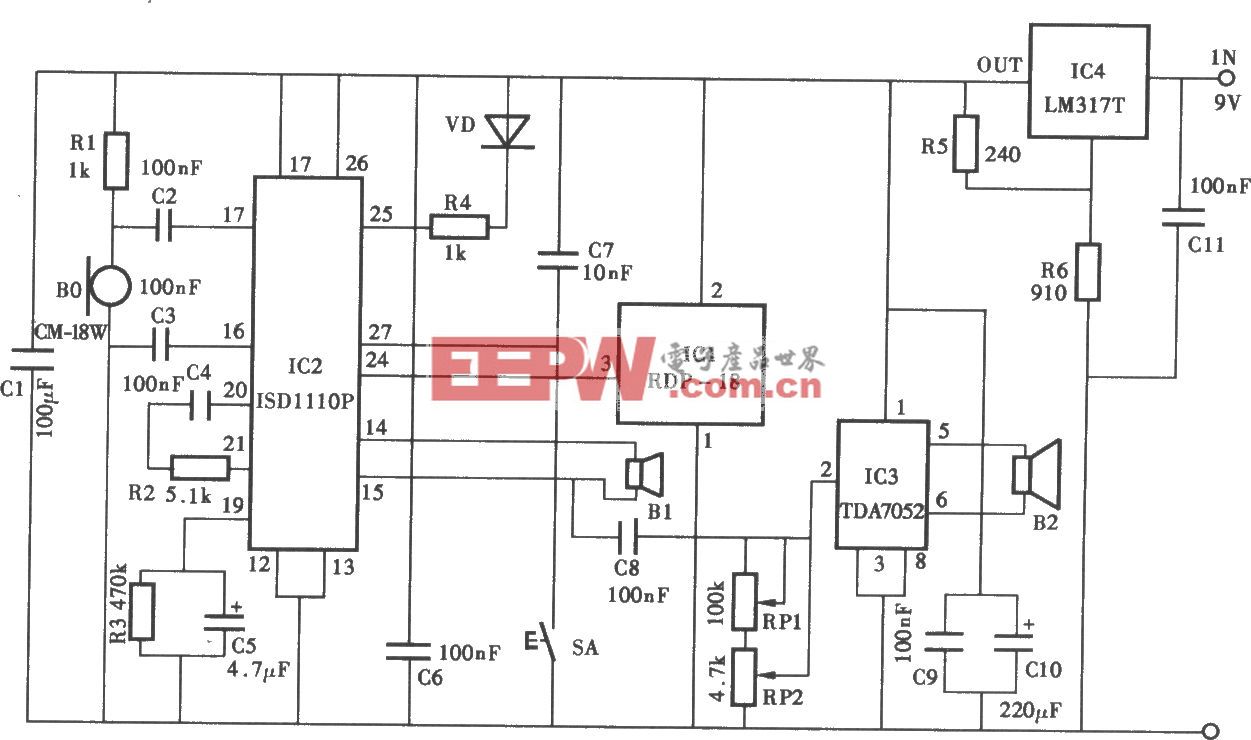

在伺服控制器上对基丁CPLD的硬件看门狗功能进行验证。DSP上电初始化完成后,先止常输出喂狗信号一段时间,然后停止输出喂狗信号,通过示波器捕获CPLD输出的系统复位信号,波形如图6所示,光标1是系统复位信号SYS_RST波形,光标2是DSP输出的喂狗信号WDT波形。从波形图前半段可以看出,WDT正常喂狗时,SYS_RST保持高电平,当WDT保持高电平一段时间后SYS_RST输出低电平,实现系统复位。复位后经过一段时间的初始化过程后,WDT开始正常喂狗。

通过以上软件的功能仿真和硬件平台上的验证,可以看出,基于FPGA/CPLD的系统外部硬件看门狗的功能得到实现,与预期目标吻合。

结语

在数字伺服控制系统中,利用其中已包含的CPLD或FPGA电路设计硬件看门狗模块,既可以满足系统对硬件看门狗功能的需求,又可以节省专用的看门狗芯片,节省电路板的空间,提高了系统的可靠性,提高了可编程逻辑器件的资源利用率,并且可以针对不同的系统上电、复位等时序要求灵活配置时间参数。经验证,没计达到了看门狗电路的功能要求,能够有效保证软件的可靠性,亦可应用于其他数字控制系统平台。

评论