基于CPLD的系统硬件看门狗设计

2.2 DSP上电过程及复位时序分析

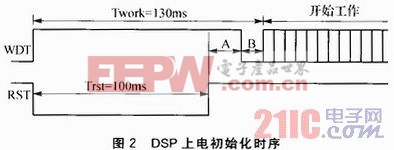

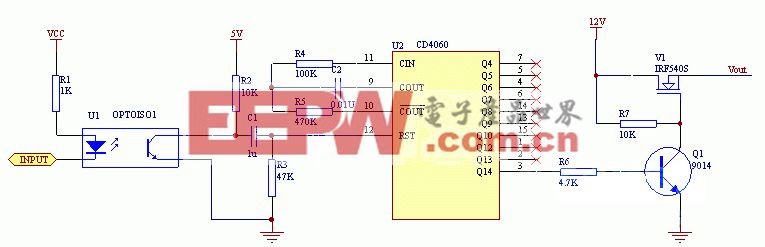

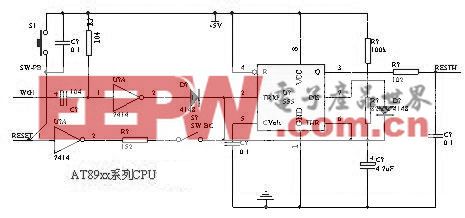

DSP上电初始化时序如图2所示。WDT是喂狗信号输出,在定时器中断或主循环中使其电平周期性取反;RST是上电复位信号。Trst是上电复位信号的脉宽,约为100 ms;Twork是从上电时到首次进入定时器中断程序的时间,约为130 ms。在主程序中首先使WDT输出低电平,则从上电复位完成到WDT变为低电平的时间A为DSP复位后自身的各项配置所占用的时间。在定时器中每次取反WDT信号,则到WDT第一次变为高电平的时间B为各软件模块及中断初始化所占用的时间。A+B为系统初始化所用的时间,约为30ms。本文引用地址:https://www.eepw.com.cn/article/190434.htm

由此可见,如果系统程序跑飞,则每次复位都要经过A、B两个过程,约30 ms的时间;那么在CPLD软件的看门狗模块中,每次在给出复位信号后都要等待DSP的初始化完成(约30 ms)后再开始对喂狗信号监测并计时。

选择看门狗定时器溢出上限以5ms为例,从程序跑飞到重新正常运行大约35 ms。设定控制系统给伺服发送控制指令信号的周期是20 ms,伺服机构常态速度10°/s,最大速度是20°/s,20 ms的时间摆动的角度是0.2°和0.4°,该角度是其控制姿态的最小步长,因此35 ms以内的热复位时间最多丢失两条指令,伺服机构在可控范同之内。此外,软件代码还有一定的优化余量,初始化时间和看门狗定时器溢出上限还可进一步减少。

2.3 看门狗设计要考虑的几点问题

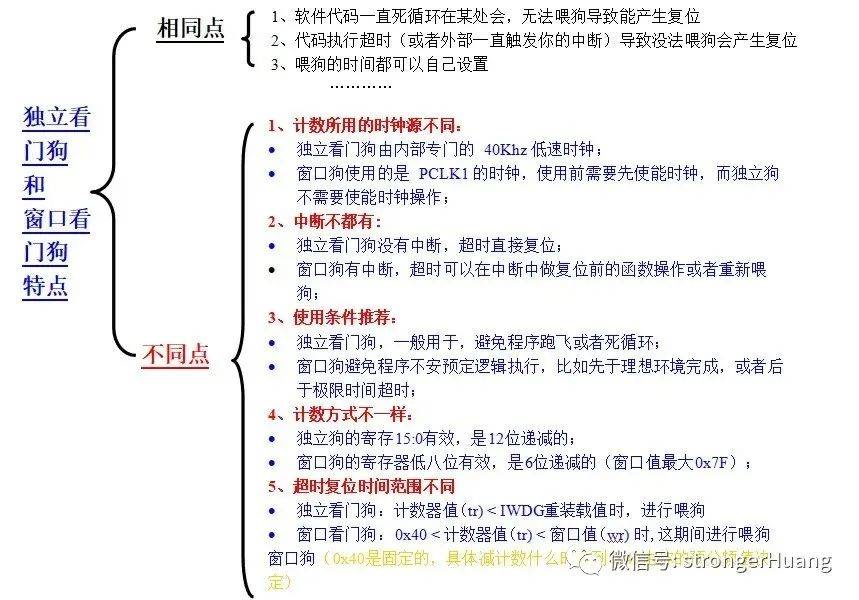

①喂狗方式:可分为电平喂狗和边沿喂狗,本设计采用后者。与电平喂狗相比较,边沿喂狗在状态机的设计中可以减少状态数量,从而节省CPLD资源,且DSP的喂狗也很容易,只要取反WDT电平,就可被认为已喂狗,简化软件代码。

②定时器溢出上限:根据具体需要灵活设定,这里暂定5 ms。

③输出系统复位信号脉宽:这里只要超过DSP所需的512个时钟周期即可,以30 MHz品振为例,时长约为171μs。

④系统上电初始化时间:系统上电复位后DSP需要一断时间初始化,而这段时间内不能喂狗,所以CPLD不能检测是否有喂狗信号,否则会造成连续的错误复位,使DSP无法正常工作,因此在CPLD代码设计时需要越过初始化阶段再去检测喂狗信号。

⑤与主控芯片的摒手信号:根据系统任务需求,可增加与主控芯片的握手信号。例如,当主控芯片需要实现总线写程序功能时,对DSP片内的Flash进行写操作,此时不能对DSP进行复位,DSP也无法输出喂狗信号,这就需要在总线写程序之前通过总线与CPLD实现握手与应答,关闭看门狗功能,程序写入完成后系统重新加电即可正常工作。为了简化功能描述,本设计术加入握手设计。

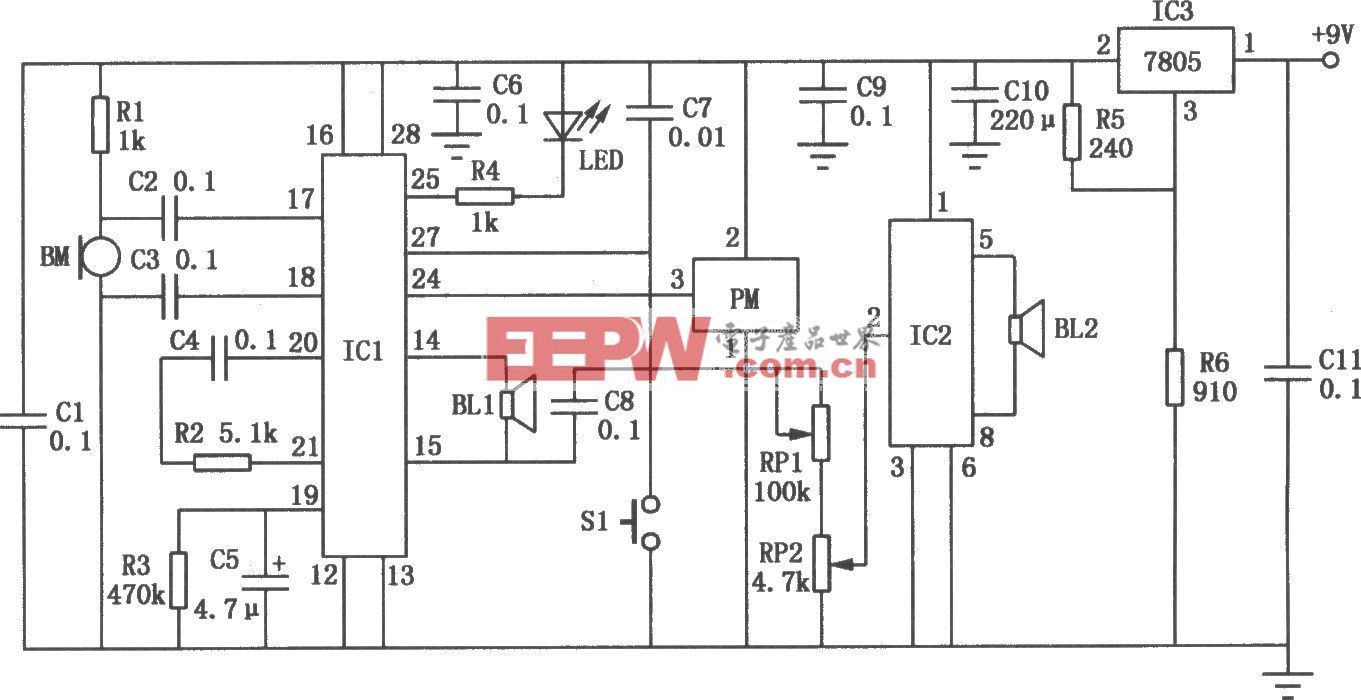

2.4 看门狗状态机的设计

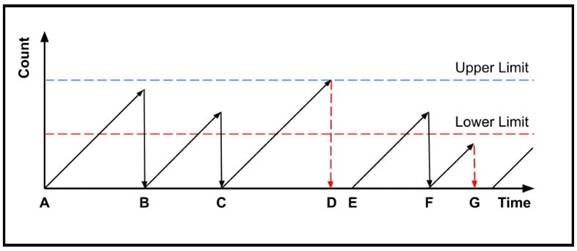

此设计采用Mealy型状态机,使用Verilog HDL语言编写代码,信号、寄存器说明如下所示:Count,时间计数器;NUM1,定时器溢出上限(5 ms);NUM2,输出复位脉冲宽度(大丁171μs);NUM3,上电复位后等待DSP初始化的时间(30 ms);WDT_fiag,3位宽移位寄存器,接收喂狗信号,比较首未位是否相等来判断是否有喂狗信号;SYS_RST,看门狗输出的系统复位信号;WAIT、IDLE、ADDING、ERROR、KEEPING,状态机的5个状态;EN,看门狗功能使能信号,高电平禁止,低电平使能。

评论