基于CPLD的系统硬件看门狗设计

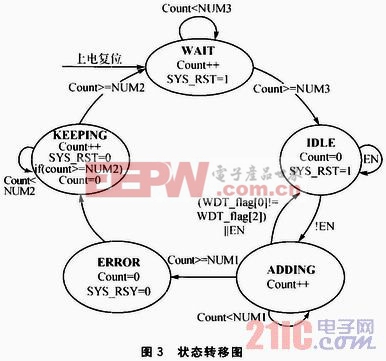

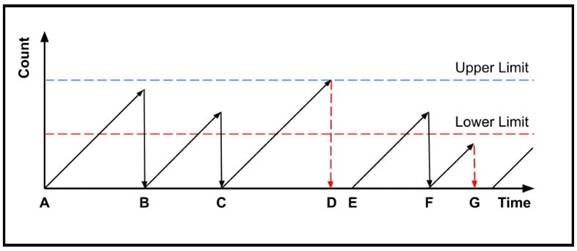

图3为状态转移图。在任意状态时如果EN使能信号被禁止,则状态机进入IDLE状态。在图上不一一标出EN的条件转移曲线。系统上电复位后进入WAIT状态,等待NUM3时间使DSP完成初始化;进入IDLE状态,如使能看门狗功能;进入ADDING状态累加计时,如果在限定时间NUM1内监测到喂狗信号,表明程序运行正常,返回IDLE状态等待下一次喂狗信号,如果超过NUM1未收到喂狗信号,认为程序已经跑飞,进入EEROR状态;EEROR状态中输出复位信号并清零计数器;进入KEEPING状态,使低电平保持一段时间NUM2,这段时间超过DSP所需的复位时间即可;进入WAIT状态,复位后重新等待DSP完成初始化,循环往复。

3 基于CPLD的硬件看门狗的仿真与验证

3.1 功能仿真

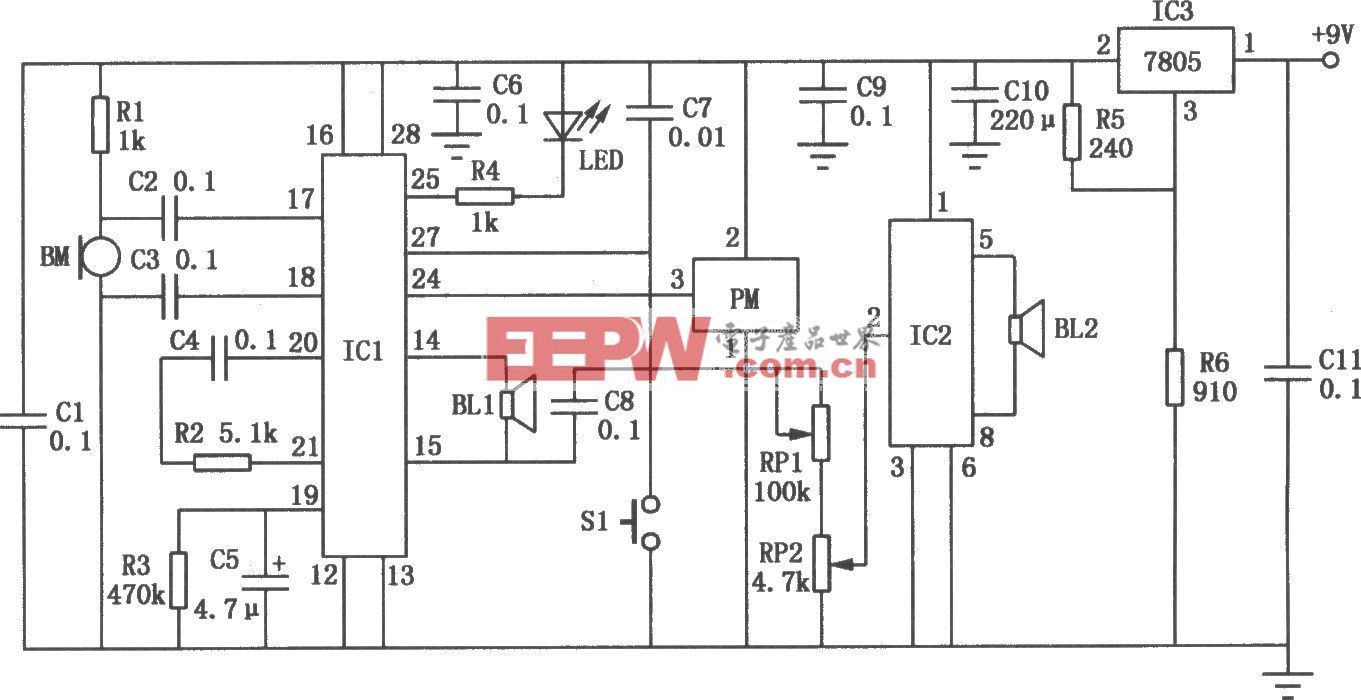

使用Modelsim软件进行功能仿真,可以看出EN信号和WDT(喂狗信号)的变化对SYS_RST输出的影响。编写测试文件对EN使能、禁止,WDT信号喂狗间隔小于、大于定时器溢出上限,以及不喂狗等情况进行仿真。

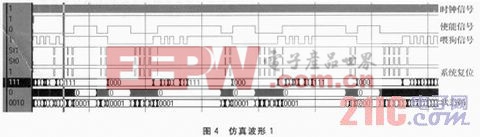

仿真波形1如图4所示。EN处于使能状态,WDT在限定时间内有边沿变化时,对应的移位寄存器也发生变化,使WDT_flag[2]!=WDT_flag[0],喂狗成功,不会输出复位信号;存SYS_RST第二个低电平处,对应的WDT超过了限定时间没有变化,故输出复位信号。

评论