无分裂结构的二维小波变换图片处理芯片设计与验证

1.3.2 列变换结构

列变换时,假设第m行的第n列完成行变换后的数据为X(m,n),将该数据寄存在寄存器D1中,下个时钟沿来临时,FIFO-A和FIFO-B中分别释放出第m-1和m-2行的第n列的数据X(m-1,n)和X(m-2,n),同D1中X(m,n)数据共同完成预测步骤生成Y(m,n)并寄存在D2中,同时从D1和FIFO-A,FIFO-B中释放出的数据X(m,n),X(m-1,n)和X(m-2,n)分别寄存进FIFO-A,FIFO-B,FIFO-C。再下一个时钟沿来临时,完成第m行第n+1列的行变换,并寄存在D1中,之后即可按照上述步骤完成第m行第n+1列数据的预测和更新,得出结果Y(m,n+1)。当FIFO把第m行数据完全释放出时,已在该FIFO寄存了第m+1行的完整数据,可以开始下一行的列变换。同理,完成预测步骤的数据寄存在D2,FIFO-D,FIFO-E中,依据预测步骤相似的原理完成更新步骤。之后依据数据的列地址的奇偶,选择不同的Y值输出。

1.4 控制结构

一般的变化模块,均采用状态机的控制方法,利用状态的跳转,来控制行变化和列变化之间的关系,完成预测和更新步骤。

而本文提出了全新的、更为灵活的直角坐标系控制法,即利用行坐标(row-c)和列坐标(col-c)形成一个二维直角坐标系,并将图片映射到直角坐标系上,每一对坐标(row-c,col-c)对应直角坐标系上图片的一个点,也对应该点的变换时刻。通过row-c,col-c的值来判断正在进行变换的行列值,来决定FIFO和变化模块的动作。利用row-c,col-c的末位来判断进行变换的行和列地址分别是奇数地址还是偶数地址,决定是进行预测步骤还是更新步骤。结合计数器,通过输入的图片的行像素值M和列像素值N,分别控制row-c和col-c的跳变。因而可以简单的通过改变M,N值的大小来改变进行变换的图片的大小。

2 结果验证

2.1 采用软硬件协同验证的结构

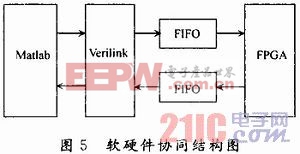

本文采用软硬件协同工作的结构,如图5所示。利用计算机端的Matlab软件从FPGA芯片中读取变换后的RGB数据,并显示在计算机显示器上。本文引用地址:https://www.eepw.com.cn/article/190283.htm

具体结构是将图片数据通过北翰科技公司的Verilink插件,从Matlab软件中送入FPGA芯片中的FIFO,小波变换模块从FIFO中依次读取数据,并进行变换,完成变换的数据通过FIFO送回Matlab软件,并显示在计算机的显示器上。

2.2 验证结果

本文采用128×128像素RGB图片作为变换图像源,在计算机的Matlab软件中,将图片转换成一维数据流,并依次通过Verilink插件送入FPGA芯片的FIFO中,在送入数据的同时,FPGA中的变换模块从FIFO中读出数据进行变换,并将变换结果通过输出的FIFO送至计算机端的Mat lab软件。在完成全部数据变换后,在计算机端将获得的数据重新排列,并转换成128×128×3的RGB图片格式,并对比显示变换前和变换后的图片效果。变换前图片如图6(a),变换并重排后图片如图6(b),图片数据高频分量和低频分量分离正确无误。

3 结语

本文提出了无分裂步骤的小波变换结构,简化了变换模块的控制系统,采用数据流模式输入数据,并且和软硬件协同的工作方式良好配对,利用FPGA和计算机完成了二维小波变换的板级验证。本文提出的结构在5/3小波变换中有效运行,并起到简化结构的关键作用,下一步将尝试把该结构运用于9/7小波变换的硬件结构实现中,并提出适合9/7小波变换硬件实现的结构。

评论