一种基于FPGA的慢门限恒虚警处理电路设计

2.1 时序产生模块

利用10 MHz时钟产生τ脉冲RM;在休止期128 τ处产生平均值打入脉冲RM128和清除脉冲RST128。原理图如图3所示。本文引用地址:https://www.eepw.com.cn/article/190185.htm

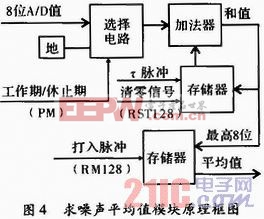

2.2 求噪声平均值模块

当休止期时,选8位I/Q信号幅度值进行累加,并对累加值进行锁存,当累加128个单元后取出平均值用RM128打入存储器锁存输出作为第一门限值,然后清除脉冲RST128清除累加值。取平均值方法:128个单元8位I/Q信号幅度值累加最大能达到15位数,平均值即为高8位值,所以取累加值的高8位作为平均值即可,原理如图4所示。

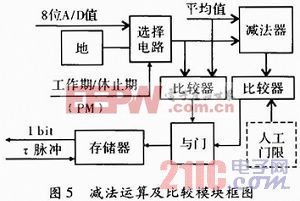

2.3 减法运算及比较模块

在工作期选取8位I/Q信号幅度值一方面与噪声平均值比较,另一方面减去噪声平均值再与人工门限比较,如果两次比较都为大于,则输出 1 bit过门限信号。原理图如图5所示。

3 仿真

慢门限恒虚警处理电路仿真波形如图6所示。PM=‘1’时为休止期,PM=‘0’时为工作期;为使仿真波形更直观、易理解,休止期恒取8位I/Q信号幅度值X[8..1]=“33”,128单元后送出平均值C[8..1]=“33”;人工门限为恒定门限,此处设为K[8..1]=“44”;在工作期,当X[8..1]=“66”和“44”时,66-3344、44-3344故1 bit=‘0’,当X[8..1]=“DC”时,DC>33,DC-33>44连续通过两道门限故1 bit=‘1’。

4 结束语

以上是在MaxplusⅡ环境中设计、编译、仿真。一般为减少积累单元数和存储计数设备,采用降低第一门限以达到高虚警率,而后面采用较高的人工门限以保证工作时的低虚警概率。该慢门限恒虚警处理电路的设计成功,为设计此类型电路提供了借鉴。采用8位二进制值累加128次,取高8位作为平均值的方法,使得电路易于实现,该方法简单、可靠。

评论