∑-△ADC的降采样滤波器的设计与实现

本设计中,k=4,c=1 617.19,f=166 kHz时Magnitude=0.999 947,满足ENOB为14 bit的要求,并为后面的设计留下16 kHz的冗余空间。

3.3 FIR半带滤波器

FIR型半带滤波器是一种特别适合实现D=2倍降采样的线性相位滤波器,其硬件结构非常简单,因此在降采样系统中的最后一级一般都采用半带滤波器。

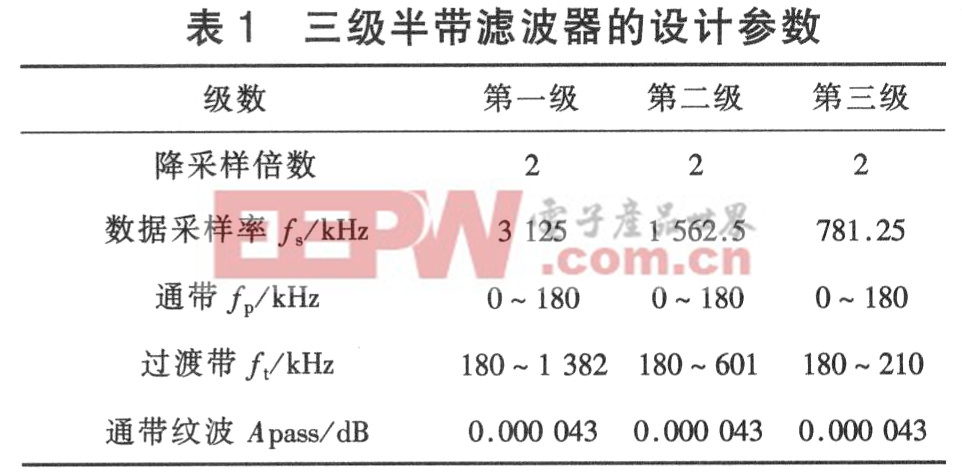

根据∑一△ADC的技术指标,可以得到三级半带滤波器的设计参数,如表1所示。本文引用地址:https://www.eepw.com.cn/article/188975.htm

通带设为O~180 kHz,是为了保证0~150 kHz带宽内均能满足指标要求。通带纹波取0.000 005(0.000 043 dB),是为了满足设计的有效位数为14 bit,并且考虑到尾数舍入等非理想因素的存在。

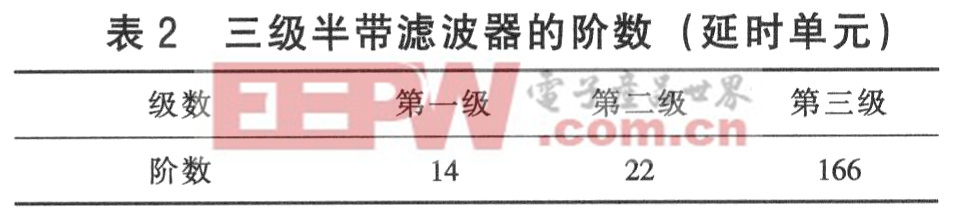

根据表1,调用Matlab 7.O中的工具箱组件filter design,得到三级半带滤波器的系数。表2分别列出了三级半带滤波器的阶数(延时单元)。

3.4 系统仿真与验证

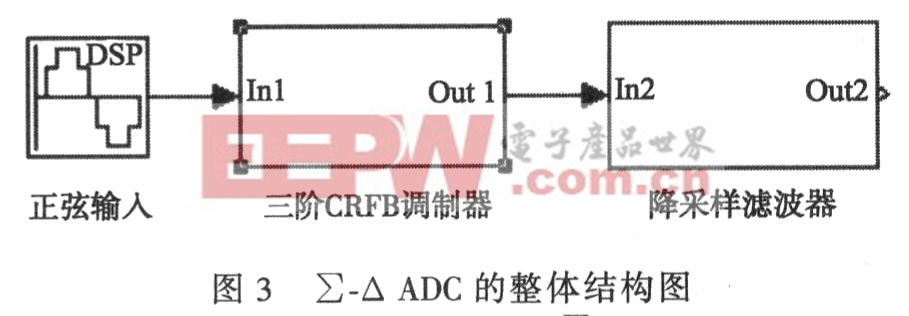

实现∑-△ADC的整体结构如图3所示,抽取滤波器由Sharpened CIC滤波器、ISOP滤波器和三级半带滤波器组成。Sharpened CIC实现16倍抽取,三级半带滤波器实现8倍抽取。

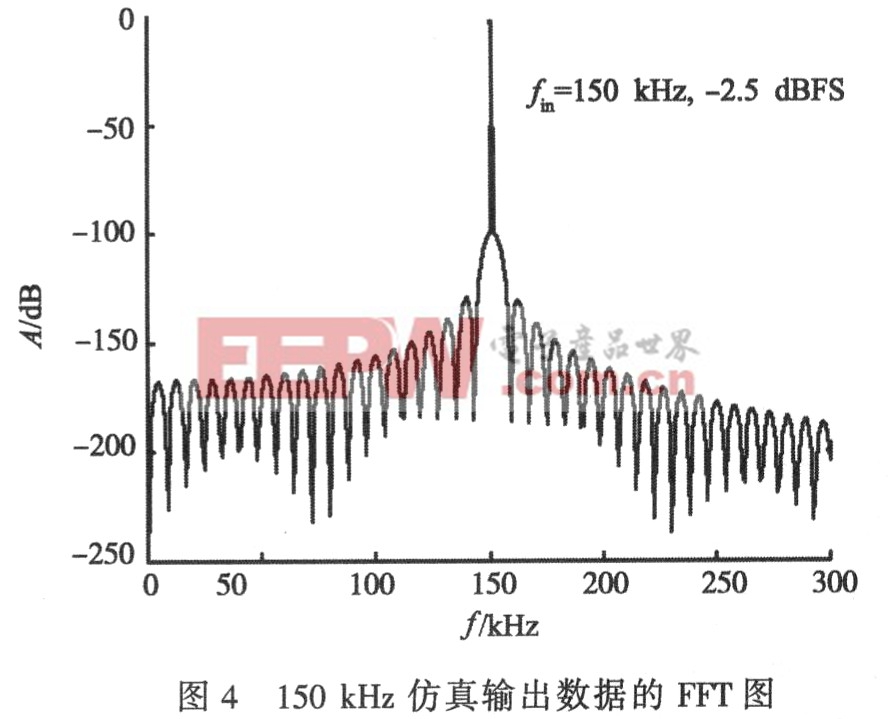

图4为150 kHz输入信号(一2.5 dBFS)仿真输出数据的FFT图。表3、4、5分别为SINAD、SFDR和THD的仿真数据。

4 降采样滤波器的ASIC设计

4.1 电路设计

本设计用Verilog硬件描述语言描述电路,采用Synopsys的Design Compiler进行综合。

4.1.1 滤波器系数优化

本设计采用CSD码(canonical signed-digit)来表示量化后的系数。和二进制代码相比CSD码采用0、l和一1来表示一个数,具有非零位的个数最少、每一个非零位的相邻位必为零的特点。

4.1.2 乘法器设计

本设计中乘法器单元的上限定为16×16,本文采用了Synopsys提供的DesignWare库中的16×16乘法器单元,该单元的设计和综合都比较成熟,通过Design Compiler综合后面积和速度的优化都比较理想。对于位数高于16 x 16的乘法器,本文以16×16乘法器单元先进行低位乘法运算,再进行高位乘法运算,最后再将高低位结果移位相加得到最终的乘法结果。

4.1.3 各级间输入输出位数的确定

评论