提高有功模式效率以满足“能源之星”要求

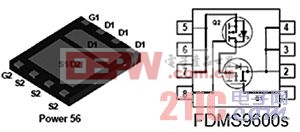

图8 Power 56的示意图与封装

占空比很小时,高边MOSFET需要非常快速地导通和关断,因此应该选择具有极小栅极电荷的MOSFET。

对于低边MOSFET,由于在开关周期内,它的传导时间要长得多,故支持的RMS电流大得多,这时I2R损耗占主要部分,导通阻抗Rds(on)成为更重要的因子。通过为高边MOSFET选择小栅极电荷(Q1)器件,为低边MOSFET选择低导通阻抗(Q2)器件,而不是高低边MOSFET采用相同的器件,可以获得更高的效率。

直通损耗

当MOSFET的漏源电压迅速上升时,感应产生的dv/dt会导致MOSFET导通。对于12V或更高的输入电压,这可能是一个问题。而且随着MOSFET的漏源电压急剧增加,dv/dt感应电压尖峰可能经由Cgd栅漏电容(米勒电容)出现在相应的栅极信号上。

如果dv/dt感应电压尖峰超过了给定阈值电压,MOSFET就会在本应该关断的时候暂时导通,对总体效率造成不良影响。必须确保所选的控制器使用了“固定死区时间”或“自适应栅极驱动”技术,或者二者兼备。

死区时间损耗

当一个同步整流器关断时,存在一个死区时间,以确保高边MOSFET等待低边MOSFET关断,从而避免交越传导。在死区时间内,低边MOSFET的内部体二极管由于反向恢复速度很慢,故需要一定的时间才能关断,这就在该时间内产生额外的功耗。

利用集成有肖特基二极管、几乎没有反向恢复时间的MOSFET来代替常规体二极管,有助于降低死区时间内的体二极管损耗。

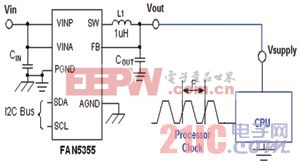

图9 通过提高频率,减少寄生效应来减小系统尺寸

寄生损耗

任何电路都会因元件封装和电路布局而存在寄生电感。由于输出功率等于输入功率减去寄生功耗,故更高的频率有助于减小器件的尺寸,把寄生电容和寄生电感效应降至最小。增加开关频率可减少元件数目,提高集成度,增强对寄生效应的控制,从而减小总体电源系统的尺寸。

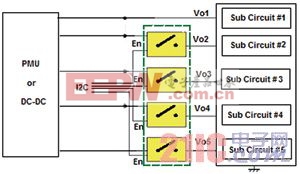

多个负载开关

在子电路进入待机模式时,负载开关可以利用使能管脚或通过I2C控制来关断其电源。减小待机电流的一种解决方案是关断系统中未使用的子电路或功能模块。系统中的电路可划分为许多子电路或功率岛区,其中每一个都整合有一个负载开关。

在待机模式下,维持供电只是为了子电路保持稍后恢复工作状态所必需的信息,图10中的子电路#1就是这种情况。所有其他子电路则关断以节电。

利用这种方法,尽管待机电流仍然大于关断所有子电路的方法,但有可能实现一个可快速恢复的待机状态。

这种方法可能带来一个工程技术挑战,即如何实现各模块启动/关断的正确时序。通过打开或切断与不同功能模块连接的负载开关,可以使系统进入待机模式。一旦GPIO或I2C发出命令,低功耗DSP就退出待机模式,解码接收到的信号,通过负载开关启动整个系统。

图10 负载开关关断子电路

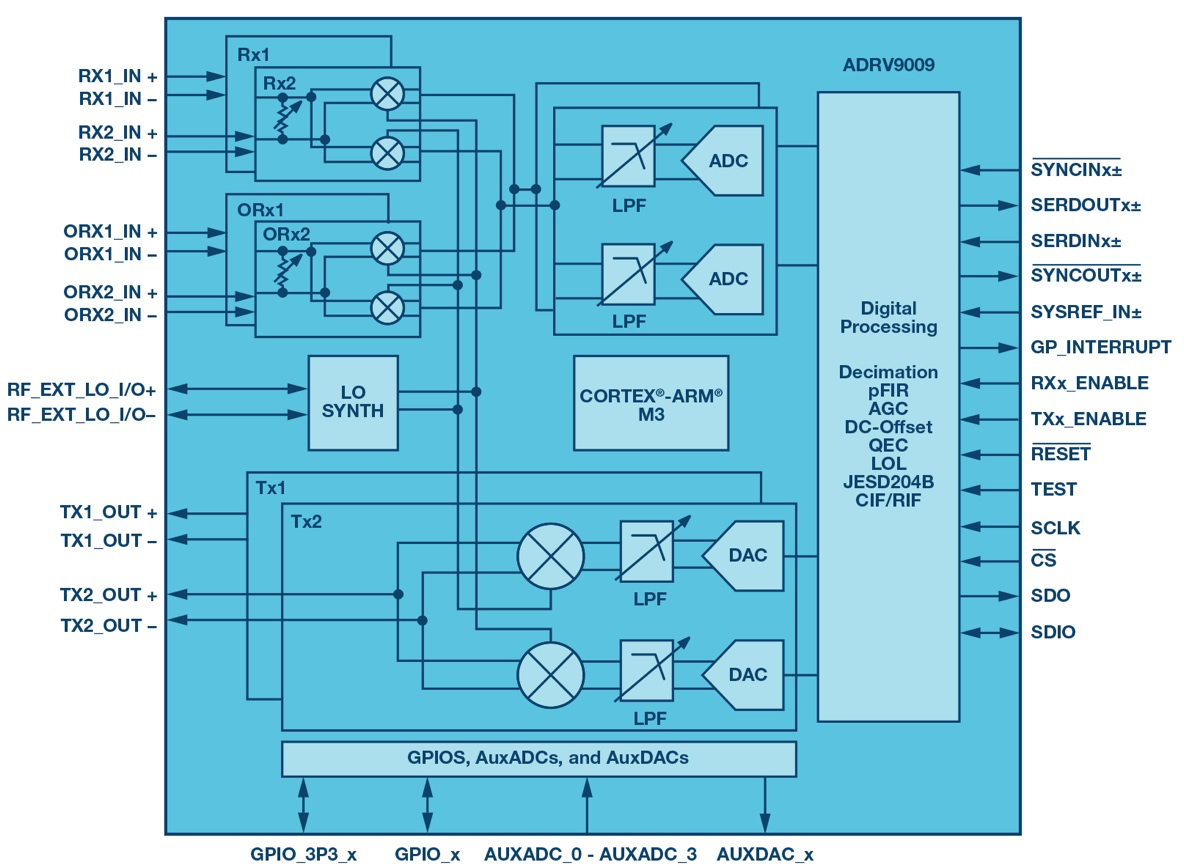

数字处理器

处理器芯片的关键在于使用低功耗技术,在待机期间减小内部工作电压,把板上振荡器频率降至低速,并优化电路,降低功耗。对于任何处于有功或待机模式下的逻辑模块,半导体行业都提供有一些相应的解决方案,可帮助降低这些损耗。

时钟门控是一项可用于降低系统有功功耗的技术。它只在有未决任务时启动特定逻辑模块的时钟。若没有未决任务,特定逻辑模块的时钟可被关断,故只减小该模块的有功功率。

还有一种更好的时钟门控解决方案,即切断未在使用的那些逻辑模块的供电。由于有功功率同时与电源电压和频率有关(V2),我们可以动态控制电源电压,或根据计算任务的强度调节处理器的时钟频率,以此来控制有功功率。若性能要求不高,系统可以降低器件的频率和供电电压。

图11 通过I2C控制实现Vout的动态电压调节

结语

关于提高满载条件下的效率,必须改变传统的思考方式,转而着眼于通过降低功耗来提高满载与轻载条件下的效率。

系统工程师必须重点关注架构级和元件级优化的改进,以实现最高效的设计和最低的功耗。特别需要注意的是低磁化电流变压器设计,通过降低轻载下铜损耗来提高效率。

此外,还需要通过顶层系统回顾,以找出给定系统中的所有损耗,然后利用带PFM或突发模式的控制器来降低轻载功耗。最后,划分功率岛区,根据需要利用负载开关来启动/关断子电路,也可以降低待机功耗。

评论