用于以太网物理层时钟同步PLL的VCO设计

4 仿真结果

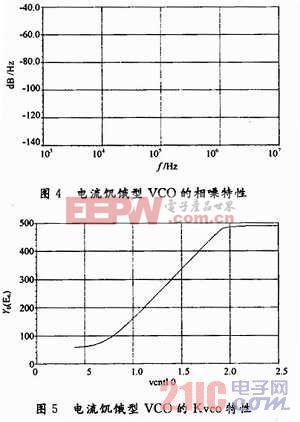

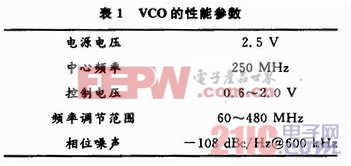

该电路的电源电压为2.5 V,使用Spectre仿真工具,VCO电路得到的输出频率与控制电压特性曲线和相噪特性曲线结果如图4和图5所示。图4为VCO的输出相位噪声曲线,可见低频的1/f噪声得到了很好地抑制。在偏离中心频率600 kHz处的相位噪声为-108 dBc/Hz。图5为VCO的输出频率与控制电压特性曲线表明,VCO的控制电压调节范围是0.6~2.0 V,线性区频率覆盖范围是60~480 MHz,压控增益为300 MHz/V,满足了以太网物理层芯片的时钟频率要求。表1给出了整个VCO的性能参数指标。本文引用地址:https://www.eepw.com.cn/article/179290.htm

5 结语

本文设计了一个适用于以太网物理层芯片时钟同步PLL的高宽带低噪声VCO,采用了具有良好抗噪能力的交叉耦合电流饥饿型差分环形振荡器。仿真结果表明,在同样输入噪声和环境噪声的情况下,本文的VCO中心频率为250MHz时,压控增益线性区频率覆盖范围是60~480MHz,在偏离中心频率600 kHz处的相位噪声为-108 dBc/Hz,较文献中传统的反相器延迟单元的环形VCO性能有明显的改善。说明了改进后的电路具有较宽的频率调节范围,较好的线性度和较低的相位噪声,完全满足以太网物理层芯片时钟同步PLL的性能要求。

评论