改进的解耦双同步坐标系锁相环的设计与实现

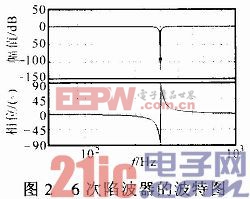

2.2 6次陷波器的设计

模拟陷波器的传递函数为:

由文献可知,当谐振频率为300 Hz,谐振点3 dB带宽为30 Hz,可得到对应的数字陷波器的传递函数为:

陷波器的波特图如图2所示。由图可见,该陷波器能够很好地滤除300 Hz的谐波。本文引用地址:https://www.eepw.com.cn/article/175888.htm

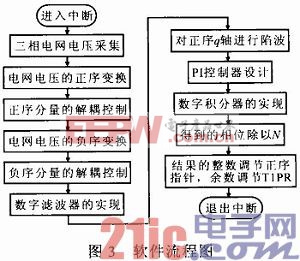

3 PLL的实现

电网电压通过LV28-P芯片进行检测,通过调理电路和电平抬升电路后将采样得到的电网电压转换到0~3.3V范围内.然后送入DSP2407。

dc相关文章:dc是什么

低通滤波器相关文章:低通滤波器原理

锁相环相关文章:锁相环原理 锁相放大器相关文章:锁相放大器原理

评论