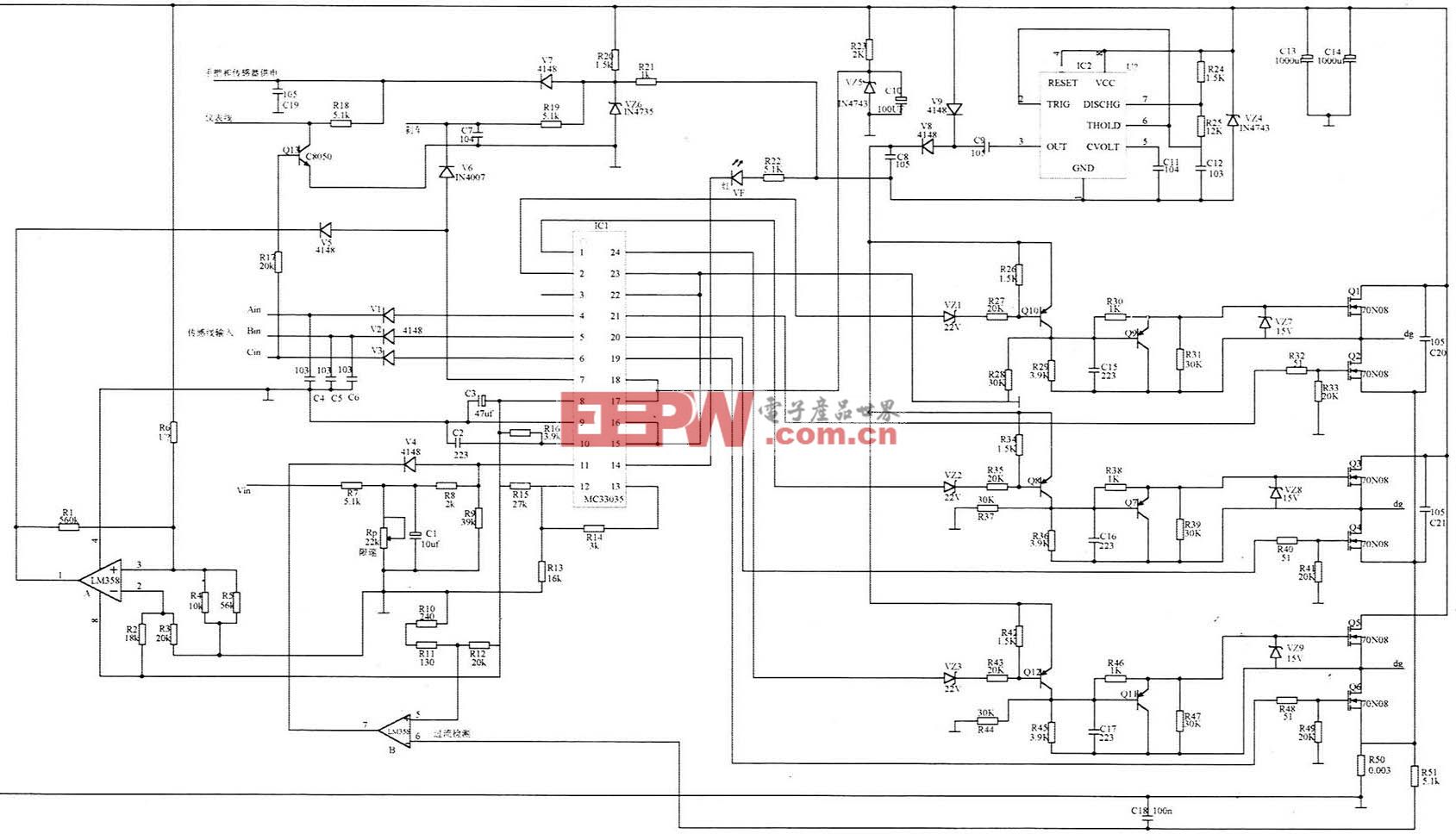

搭配电感拓扑,利用小讯号MOSFET降低电源转换功耗

该设计采用的控制器还整合0.8伏特精密基实缪乖矗用于输出电压调节。降压转换器的输出返回至FB接脚。由R41+ R39和R38组成的电阻分压器调节输出电压,可由公式12计算:

VOUT=0.8V×(1+(R41+R39)/R38)。。。(12)

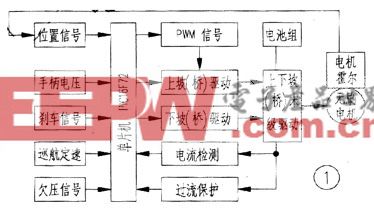

假设控制器以a定频率工作,在高电流情况下可轻控制DC-DC降压转换器的输出电压,但于低电流情况下对控制要求则升高,须大幅调整工作L期,或将控制器转换为另一种控制模式,如高负载模式。该控制器有强制连续、高负载和脉n跳跃叁种工作模式;其中,高负载模式具有高效率优点,但涟波更大且电磁干扰(EMI)严重,最合适的模式须取决于终端应用的规格和需求。

可编程设计的开关频率范围为250k? 750kHz,频率由电阻R30决定,控制器也可将内部振U器与外部时源同步(MODE/PLLIN,接脚1)。该模式下,RC网路须与接脚2(FREQ)相连,做为锁相路(PLL)滤波器。

掌握电压/电流涟波设计 中功率DC-DC转换效率增

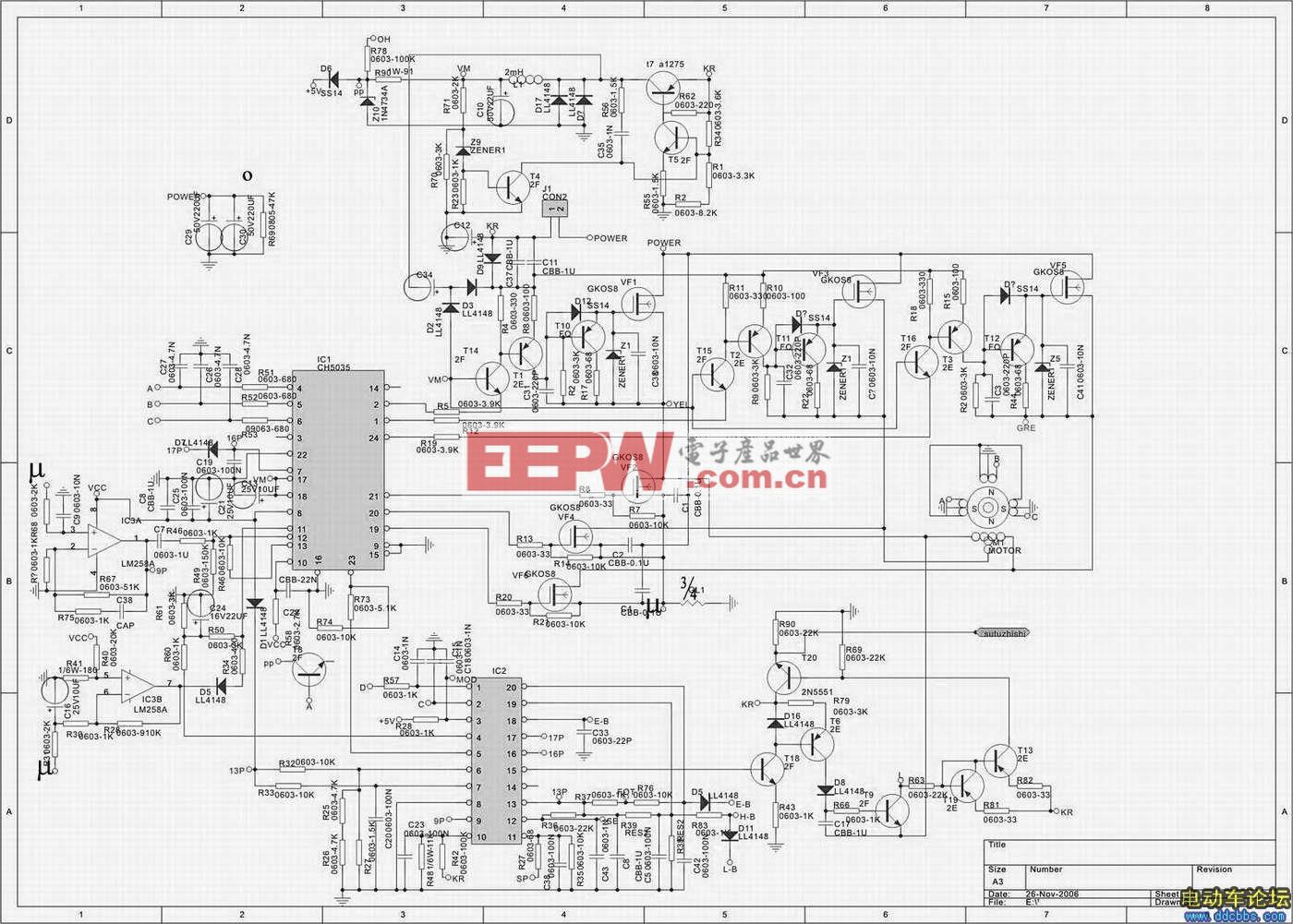

DC-DC转换器有多种应用,具备外部MOSFET级的降压转换器控制器拓扑常用于运算和消费性电子产品中。新一代系统单晶片(SoC)解决方案须用到许多独立的电源电压,以提供主机板、笔记型电脑、平板装置、电视或机上盒(STB)等装置优异的电源管理方案。

由于电源围最高可达数百瓦,最低仅数瓦,在桌上型电脑中,DC-DC转换器须提供高达100安培的电流和130瓦功率,开关级MOSFET裼梦匏鸱庾(LFPAK)或QFN 5×6封装的趋势也逐渐盛行,一般笔电和小笔电的功率需求相对较小,功耗围为18~55瓦。开关MOSFET主要裼SO-8和QFN 3×3封装。电视、机上盒或平板电脑等消费性电子的应用,功耗要求为7~15瓦。

对于中等功率围而言,目前可用QFN 3×3、QFN 2×2或SOT457等具有更小封装的小讯号MOSFET来替代SO-8。为达到所需的电流涟波,须仔细选择用于降压转换器的电感值。电流涟波更大,则输出电压涟波也更大;涟波增加,则电感更小、输入电压更高,若开关频率降低,则将进一步增大。

ΔIL可由下列公式13算出:

ΔIL=VIN/L×ton=VOUT/L×toff.。。(13)

其中,T=ton+toff=1/f

得到公式14:

ΔIL=(VOUT/L)×(1–VOUT/VIN)×1/f.。。(14)

此时表示L=(VOUT/ΔIL)×(1–VOUT/VIN)×1/f。在极端情况下,电路会以连续模式的极限运行,电流在再次增大之前会完全降为零,可得出公式15: ΔIL=2×I(均值)。。。。。。(15)

代换ΔIL后,L=VOUT×(1–VOUT/VIN)/2×I(均值)×f

实际上,涟波电流ΔIL一般约为最大电流的30%,输出电压的涟波不仅取决于电感和ΔIL,还与输出电容的电容值有关,电容愈大,涟波愈小。图8为流入电容的电流波形图,无损耗电容的计算方式如公式16:

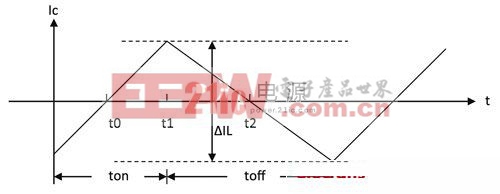

图8 电容电流与时间的关S示意图

。。。。。。(16)

对于t0至t1,IC=ΔIL/ton×t;对于t1至t2,IC=ΔIL/toff×t。

电容涟波电压如公式17所示:

。。。。。。(17)

当T=ton+toff=1/f时,可进一步得出公式18:

VC_ripple=ΔIL/(C×8×f)。。。。。。(18)

此外,实际电容须考虑等效串联电阻(ESR),因此可得出公式19:

VC_ripple=ΔIL×(ESR+1(8×F×Cout))?(19)

做为开关的MOSFET则须考虑两个损耗过程,一个是欧姆损耗,由剩余导通电阻RDSon造成;第二个损耗产生于开关瞬变。由于MOSFET并非理想的电源开关,从关闭到开启状态(或开启到关闭)仍存有短暂的导通时间。

RDSon损耗也称I2R损耗,可通过公式20计算(lout表示RMS值):

。。。。。。(20)

其工作L期为D=ton/T,项数1+δ包含与MOSFET的RDSon有关的温度。δ典型值为δ=(0.005/℃)×(Tj–25℃)

低端开关则与其相似,由于当高端开关关闭时,同步MOSFET接通,因此I2R损耗可由公式21计算:

。。。。。。(21)

汲极电流/电压影响MOSFET开关性能

至于转变损耗,仅高端开关受此机制影响,塬因在于所裼玫男流二极体(图8中的D1)已接通,它将同步MOSFET上的电压降至较小的正向电压VF,若电路不含续流二极体,则情形有所不同。MOSFET的RDSon损耗须计入本体二极体的损耗,若不使用续流萧特基二极体,则效率通常受较高的VF和本体二极体反向恢褪奔涞挠跋臁

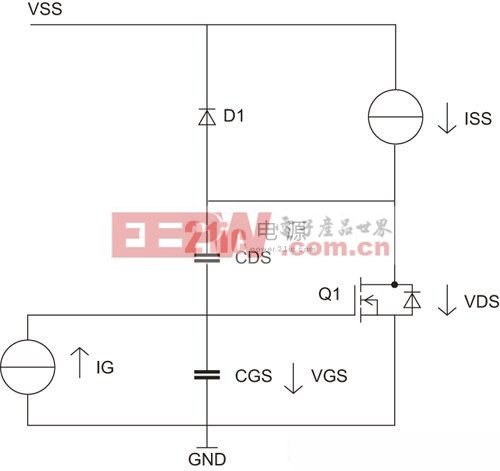

图9表示MOSFET开关性能的测试电路,包含闸极至源极CGS、汲极至闸极CDG的寄生电容。电流源IG为控制闸极,在源极另一个电流源与一个续流二极体并联,随后连接VSS,只要MOSFET为关闭状态,电流便流经该二极体。导通过程中,若电流源IG打开,CGS的电压线性上升,直至达到闸极-源极阈值电压VGS(th)。此时开始有汲极电流通过,表示MOSFET在t0阶段依然处于关闭状态。

图9 MOSFET开关性能测试塬理图

汲极电流在t1阶段上升。同时闸极电压上升,直至达到VGS(pl)。VGS(pl)通常称为MOSFET的_阶电压。它在资料手册中一般不会明确提及,但可由塬理图中的闸极电荷与闸极-源极电压衍生出来,在详细资料手册中可找到。t0和t1阶段过后,电荷为Q0=Vpl×(CGS+CDS)。

在下一个t2阶段,汲极电压下降,闸极-源极电压VGS保持a定,为VGS(pl)。电荷Q1以相反方向对CDS充电,Q1=VSS ×CDS。CDS有别于双极电晶体,它与米勒电容类似,且对MOSFET的开关性能有巨大影响。在t3阶段闸极电压再次增大,直到达到所需的最大闸极电压,此时电流源被截流。FET的RDSon进一步降低。闸极驱动器提供额外的电荷Q2如公式22所示:

Q2=(VGS(t4)–VGS(pl))×(CGS+CDS)。。。(22)

总电荷则为QG=Q0+Q1+Q2,对功率MOSFET而言,该电荷可轻易超过100nC,计算方式如公式23:

IG=QG/ts.。。。。。(23)

由此可见,闸极电流可经计算达到开关时间ts,若须较短的转换时间,就要使用强大的驱动器控制MOSFET,以保持较低的开关损耗。在t1阶段,MOSFET具有完全的输入电压,此时汲极电流增加;在下一个t2阶段,ID定而汲极-源极电压VDS下降,主要开关损耗均产生于这两个开关阶段;而t3阶段损耗极小,可忽略,RDSon下降到最小值,此时达到最终VGS电压。

开启时的开关损耗发生于t1和t2阶段,最主要损耗发生在t2,此时MOSFET的闸极电压保持在台阶电压V(pl)。损耗可由公式24计算:

PSW(on)=VIN×I/2×(t3+t1)×1/T?(24)

转换器的开关频率为fSW=1/T,MOSFET的关断特性与开启时类似。总开关损耗可由公式25计算:

PSW=VIN×1/T×(Imin/2×ton+Imax/ 2×toff)。。。。。。(25)

开关时间将取决于驱动器的电流驱动能力和MOSFET的闸极电阻,假设开启和关断时的驱动电流相等,则开关时间为tSW=QG/Idrive

LTC3851 tSW可由公式26估算:

tSW=QG×Rdrive/(Vdrive–VGS(th))。。。(26)

控制器的Rdrive约为2欧姆,与其有关的电压是驱动器电压INTVCC–V(th)。

小讯号MOSFET转换/散热效率俱优

显而易见,小讯号MOSFET适合中等功率DC-DC转换,若闸极-源极电压为4.5伏特,可提供15毫欧姆的RDSon,对SOT457元件而言,这是非常小的电阻,可提供更优异的电源转换效率,再加上裼猛片引线框架,让封装尺寸缩小,亦可具有良好散热性能。

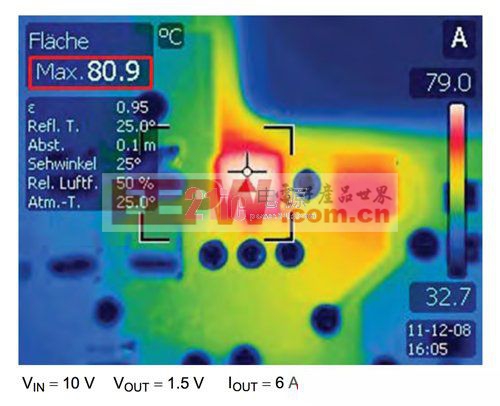

图10是一张热成像照片,说明此一参考设计的DC-DC转换器PCB的输出电流为6安培,并将电压从10伏特降为1.5伏特,由于工作L期低至0.15,低端开关比高端开关散发更大的热量;而该元件的温度约为80℃,可推断结点温度Tj通常比封装表面高5?10℃,故本测试中,Tj低于90℃。

图10 内建DC-DC转换器的PCB热成像照片

高效率中等功率DC-DC转换器可裼眯⊙逗MOSFET设计,P通道MOSFET作为高端开关,与萧特基二极体共同组成简单转换器,其中,萧特基二极体须具低正向电压,裼媒舸招捅馄焦β史庾埃若还须进一步提升效率,则要改裢步DC-DC转换器。

评论