基于DP标准的扩频时钟发生器系统参数研究

把f=30 kHz,△f=8.1/2 MHz(或13.5/2 MHz),KV=970 MHz代入式(3),得到,IS/(C1+C2)=250 A/F(或417 A/F),考虑到滤波器电流稳定性及电容大小,取Is=2.5μA,C1+C2=10 nF(或6nF),这里的电容值表示实际应取电容量级,不是最终值。

(3)确定环路带宽K

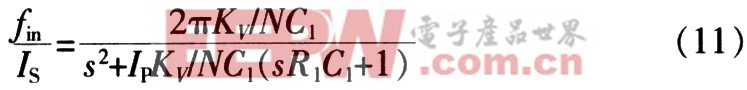

环路带宽需综合考虑噪声抑制和锁定时间等因素。这里的调制滤波器可形象地认为是人为的在压控振荡器的输入端加入一个噪声源,这个噪声虽然对于时钟输出是必须的,但经环路后在鉴频鉴相器的输入端却是需要被滤去的,否则将影响锁相环环路的稳定性。滤波器只考虑R1,C1,经简单推导,得到传递函数如下:

式中,fin是鉴频鉴相器的输入,IS是调制滤波器的电流。

式(4)简单描述鉴频鉴相器的反馈输入与调制滤波器电流的关系。该传递函数具有低通特性,有s1和s2两个极点,通过假设s1>>s2得到s1=K,s2=1/R1C1=ωz,式(11)可表示为:本文引用地址:https://www.eepw.com.cn/article/169452.htm

为抑制调制滤波器对环路的影响,除增大充电电流减小直流增益外,通过减小带宽K和锁相环的零点ωZ也能得到一定效果。但同时还需考虑对于压控振荡器的高频噪声。通过行为级仿真,带宽K取75 kHz。

(4)相位裕度取值

相位裕度取60°,对应γ=4,零点ωZ应处于K/4的位置,即37.5πkHz,而极点ωP1应处于4 K的位置,即600π kHz。在采用三阶滤波器时,需考虑引入的极点对相位裕度的影响,故γ一般取为5~6。

![]()

(5)滤波器中电流的选择

滤波器充电电流IP=500μA。该电流值受限于滤波器电容的取值。

(6)计算RP(R1+R2)

对应于810 MHz和1 350 MHz的输出频率,分别取,N值为900和1 500。

计算C1=9.1 nF或5.4 nF,C2=0.6 nF或0.364 nF。

(8)R3和C3的取值

选择合适的R3和C3值以对毛刺进行滤波衰减。

由相位裕度的影响可知,R3和C3必须满足:R3>2RP,C31/10C1。其中,fref是输入参考频率,是额外的衰减值(dB)。取ATTEN=10 dB,fref=900 kHz,得到R3=3 kΩ,C3=174 pF。

以上计算所得参数还需满足使调制滤波器可进行三角波调制的条件,另外还需考虑减少用来控制滤波器参数的传输门及稳定性等因素。

3 系统仿真

这里采用的系统参数设计带有一定的经验性,但其理论依据是线性反馈控制系统理论,图5、图6、图7和图8列出了使用PLLsim软件对环路进行仿真的结果。

4 结束语

基于DP标准的发射端扩频时钟发生器的性能依赖于初始参数。根据线性反馈控制系统理论并结合实际经验,对该组系统参数进行分析,在综合考虑数模混合电路的功耗、面积、性能等因素的基础上,设计锁相环的整体参数及各模块的性能参数。给出一组性能较优的参数值,该组参数为电荷泵和压控振荡器提供了稳定的电流和电压。另外,采用三角波调制压控振荡器控制电压的方法减小电磁干扰。最后,使用PLLsim软件对环路进行仿真,得到了较满意的效果。

评论