基于单片机的LED显示屏硬件设计方案

否则将要发送的信息发送并清零发送结束标记。这样设计的发送程序, 其目的是将发送等待不限制在接口底层, 而是给上层一个决定是否等待发送结束的机会。

u8 uart_put_c(u8 ch){

if(! TI)return 1;

TI = 0;SBUF = ch; return 0;

}

同样, 接收程序也给上层一个选择等待的机会。接收函数首先判断接收FIFO 是否为空, 如果为空或输入指针参数错误, 则直接返回错误, 否则才从FIFO 中读取数据并将数据存储到指针指向的地址, 然后返回成功。

u8 uart_get_c(u8 *ch){

u8 i;

if(! ch)return 1;

if((i = (uart_rd+1)0x0f) == uart_wr)return 1;

uart_rd = i; *ch = uart_buf[i];return 0;

}

3.3 闪存接口

闪存的存取有特殊的时序, 闪存的内部结构也和具体应用要求有很大的不同。因此闪存的接口需要仔细设计。

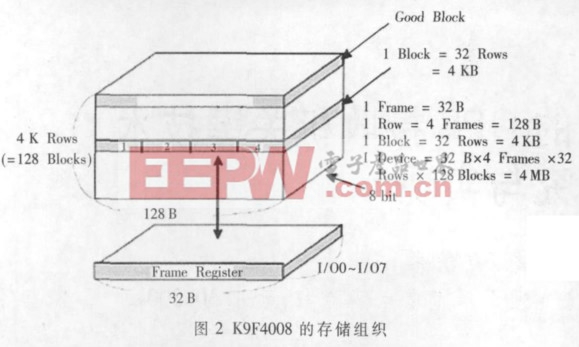

K9F4008 闪存芯片的存储结构组织如图2所示。

K9F4008 闪存的存储以块为单位, 每个芯片共有128 块。每块有32 行, 每行有4 个帧, 每帧含有32 B.全部芯片为512 KB。

闪存接口提供的闪存初始化函数中就包括对这样情况的处理。初始化函数要从闪存的第一个块中读出一个块映射表, 该表下标是逻辑扇区, 表内每项存储的是该逻辑扇区对应的物理块编号。初始化函数在必要时对闪存进行读写校验, 然后将坏块从表中删除。再寻找新的良好块, 将其编号填入到对应逻辑扇区的表项中。这样对应用来说, 只见到连续的扇区编号, 而不知道扇区究竟对应到那个块。

闪存的接口头文件Flash.h 如下:

#ifndef _K9F4008_H_

#define _K9F4008_H_

void read_log_page(u8 sector,u8 page,u8 xdata *buf);

u8 prog_log_page(u8 sector,u8 page,u8 xdata *buf);

void erase_log_blk(u8 sector);

bit flash_init(void);

#endif

实现闪存的接口, 首先就是依据说明书的时序定义闪存的基本操作。这里是以宏定义实现基本操作的。

#define W_CMD(cmd_)

bCLE=1; bWE=0; P2=(cmd_); bWE=1; bCLE=0

#define W_ADDR(addr1_,addr2_,addr3_)

bALE=1; bWE=0; P2=(addr1_); bWE=1;

bWE=0; P2=(addr2_); bWE=1;

bWE=0; P2=(addr3_); bWE=1;

bALE=0

#define W_DAT(dat_) bWE=0; P2=(dat_); bWE=1

#define wait_RB while(! bRB)

#define l2p(x_) fat_tbl[(x_)]

3.4 EEPROM

内部集成的EEPROM 是与程序空间分开的, 利用ISP/IAP 技术可将内部DATAFLASH 当EEPROM,擦写次数10 万次以上。EEPROM 可分为若干个扇区, 每个扇区包含512 B.使用时, 建议同一次修改的数据放在同一个扇区, 不是同一次修改的数据放在不同的扇区, 不一定要用满。数据存储器的擦除操作是按扇区进行的。

sfr IAP_DATA = 0xC2; //Flash data register

sfr IAP_ADDRH = 0xC3; //Flash address HIGH

sfr IAP_ADDRL = 0xC4; //Flash address LOW

sfr IAP_CMD = 0xC5; //Flash command register

sfr IAP_TRIG = 0xC6; //Flash command trigger

sfr IAP_CONTR = 0xC7; //Flash control register

根据使用说明对EEPROM 的寄存器进行定义。

评论