视频信号数字化光纤传输实验装置的研制

2.6 D/A转换及视频信号输出

2.6.1 D/A转换部分

采用美国模拟器件公司出品的AD9708,它属于高性能、低功耗CMOS数模转换器,能提供出色的交流和直流性能,支持最高125 Mz/s的更新速率。工作时钟设为16 MHz,由FPGA提供。本文引用地址:https://www.eepw.com.cn/article/165897.htm

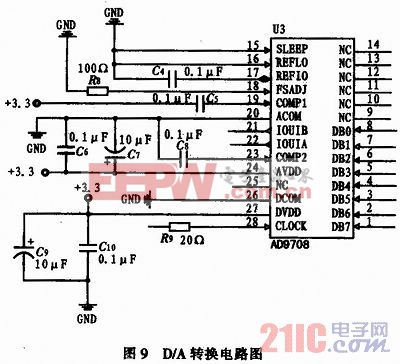

AD9708的外围电路如图9所示。其中REFLO是转换基准的参考地,此脚接地禁用内部参考电压。COMP1是噪声衰减模式设置端,此处串接0.1 μF的电容能达到较好的转换效果。R9是终端匹配电阻以消除高频振荡。C9和C10用以滤除数字电源纹波,C6、C7用以滤除模拟电源纹波。并行数据由DB0~DB7输入,转换后的数据由IOUTA输出。此处输出的信号须经运放放大后,才能满足通用性视频显示器的技术要求。

2.6.2 模拟放大及视频信号输出

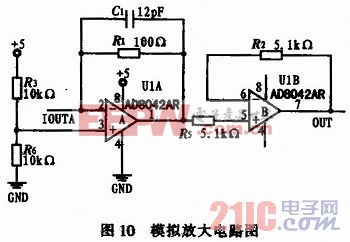

采用AD8042实现信号的放大,如图10所示。ULA将AD9708输出的电流信号转换为电压信号,其中C1主要作用是去除高频干扰。ULB作为电压跟随器,用于阻抗匹配。要求的输出阻抗是75 Ω,电压跟随器使输出阻抗为0,再串联一个75 Ω(在ULB的7脚之后,图中未标出),来满足匹配要求。

3 程序设计及仿真

系统采用VerilogHDL语言进行程序编写,在QuartusⅡ环境下编辑仿真。FPGA内部时钟由32 MHz晶振提供。FPGA的工作是:1)提供D/A转换芯片AD9708、A/D转换芯片AD9280、并串转换芯片LV1023的工作时钟和串并转换芯片LV1224的参考时钟,都是16 MHz;2)发送端对数据进行8B10B编码,并将转换后的数据传送给串化器;接收端获取串并转换后的十位数据,进行解码,还原为编码前的八位数据,并将解码后的数据传送给数模转换芯片。

3.1 8B10B编解码

8B10B编码是目前高速串行通讯普遍采用的编码方式,8B10B编码的目的是将八位数据转换成10位的数据,并使转换后的数据流中“0”和“1”的数量平衡,避免发送过程中因过多重复的出现“0”或“1”而发生的错误,提高线路传输的性能,有利于接收器更准确的捕捉同步时钟,而且采用特定的码元可以使接受端更准确地对准码元。

8B10B编码可以看成是5B6B和3B4B编码的组合,组合过后有些编码可能有两个值,“1”和“0”的差值称为平衡度,用RD-表示平衡度为+2或0,RD+表示平衡度-2或0。将转换后的数据接平衡度分为RD-和RD+两列。设变量DISPIN表示正在转换的数的平衡度,DISPOUT表示下一个转换的数的平衡度。初始时设DISPIN与DISPOUT相等,先从RD-中开始转换,如果转换后的数“0”和“1”的数量相等,继续在RD-列中转换下一个数,如果“0”和“1”的数不等,则转到RD+列中转换。同理在RD+列中,如果“0”、“1”个数相等则继续在RD+中,否则换到RD-中。

解码部分将10位数据的前六位和后四位分别按照5B6B和3B4B的列表解码即可。

3.2 仿真

设计程序经QuartusⅡ综合器编译综合成功后,可以对输入数据、中间产生的数据、输出数据进行仿真。装置采用的8B10B编码方式,分为3B4B和5B6B进行编码。解码部分依照编码时相同的分发将十位数据分为4B和6B分别解码。解码后再按顺序组合成8位数据。程序以4B3B、6B5B分别查表的方式实现。

程序仿真图如图12所示,adin是编码之前的八位数据,设为逐次加一的计数数据,为了方便比较,图中用十进制表示。编码后的十位数据为data10b,adout是解码后的数据。可以看到虽有延迟,解码后数据仍为计数数据。因此程序可以准确地实现解码功能。

4 结束语

全电视信号中除了视频信号外,还包括音频信号,其声音信息的传输与转换处理,是应用领域中不可缺少的内容与完备。除了单向通信外,收发设备之间相互进行信息交换,实现双向通信、完成反向控制功能,在光纤通信应用领域中获得广泛应用和普及。这些课题的技术性拓展与转换,移植到相关实验教学的应用中,一定有其积极的作用和意义。

评论