视频信号数字化光纤传输实验装置的研制

2.3.2 同步分离部分

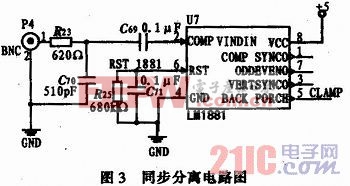

全电视信号中除了图像信号外,还包含复合同步信号:由行、场和色副载波等组成;这些同步信号与图象、声音信号按照一定规格的国际制式编制标准构成,使得整个视频信号完整协调统一。所以在进行传输处理视频信号时,要对其中的同步信号实施技术分离,以便相应控制处理,具体电路采用LM1881集成芯片实现。该芯片可从全电视信号中提取与分离出:行和场、后延同步、奇偶场的图像信息。图像的复合视频信号直接由系统的相关设备提供,芯片的BACK PORCH管脚在视频信号消隐期间产生后延脉冲,该脚接到A/D转换器AD9280的CLAMP端口即19脚,使A/D转换器在信号的消隐期间处于钳位工作模式,可将消隐电平钳位在0电平的位置,从而使得采集处理信号时能够正确得把握各个信号间的时序关系和逻辑关系,完成同步信号分离的功能。本文引用地址:https://www.eepw.com.cn/article/165897.htm

分离电路采用美国国家半导体器件公司出品的集成LM1881来实现,电路如图3所示。

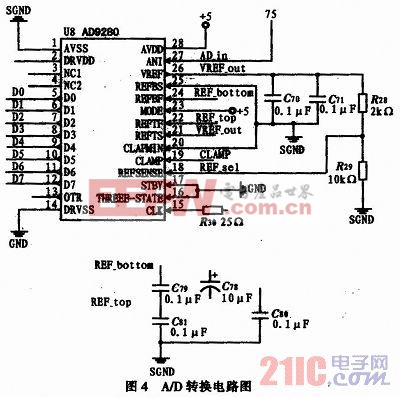

2.3.3 A/D转换部分

模数转换电路同样采用美国模拟器件公司出品的集成AD9280来实现,其工作时钟频率设定为32MHZ,由FPGA提供。信号由AIN管脚输入,D0~D7输出转换后的8位二进制数据。STBY和THREE-STATE脚接地,以保证芯片正常工作。CLAPMIN接地,把消隐电平钳位为0电平,其电路如图4所示。

2.4 信号发送部分

由FPGA处理后的数据要通过光纤发送,不需先将并行数据转换为串行数据,再将串行数据转换为光信号。

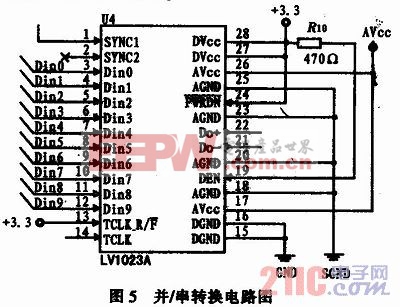

2.4.1 并/串转换

电路采用串化器DS92LV1023集成芯片实现,电路如图5所示,其对应接收端由解串器DS92LV1224集成芯片完成。DS92LV1023可以将10位并行数据转换为串行差分数据流,该差分数据流可以由DS92LV1224还原为10位的并行数据。这一组芯片内部有锁相环,可以为数据输出自己匹配时钟。串化器LV1023参考时钟选为32MHz,数据在该时钟频率下输入,其芯片内部匹配产生数据输出时钟,每一个10位并行数据转换为12位串行数据,其中多出一个起始位和一个终止位,所以有效频率为320 M。解串器的参考时钟定为16MHz,以满足数据传输需求。

由于视频信号是实时不断的,所产生的数据流连续进行,所以电路不能设置进入高阻态或省电模式,因此LV1023的DEN和PWRDN都置高电位。

串行数据的准确传输需妥串化器和解串器同步,该组芯片有2种同步方式:

1)快速同步 串化器LV1023发送一组同步信号,由连续是6个“1”和6个“0”组成,发送同步信号是由SYNC1和SYNC2控制的,当SYNC1或SYNC2置高电平持续时间超过6个时钟周期时,则开始连续发送同步信号,当解串器LV1224接收到同步信号后便开始试图锁定时钟信号,锁定完成之前LOCK保持高电平,锁定完成后LOCK跳变为低电平。

评论