视频信号数字化光纤传输实验装置的研制

2)随机同步方式 该组芯片在没有同步信号传输的情况下仍然可以完成锁定,这使该组芯片在开放场合得到应用。随机同步时,串化器不发送同步信号,解串器直接对差分数据流进行锁定,该锁定方式会受到初始时数据和时钟的相位影响,也会受到数据本身的影响,当一个特殊的数据图样反复出现时,解串器可能出现锁定错误,称为RMT。但当同步丢失后,解串器会重新锁定时钟,恢复同步。

由于该电路采用随机同步方式。串化器的SYNC1和SYNC2悬空。

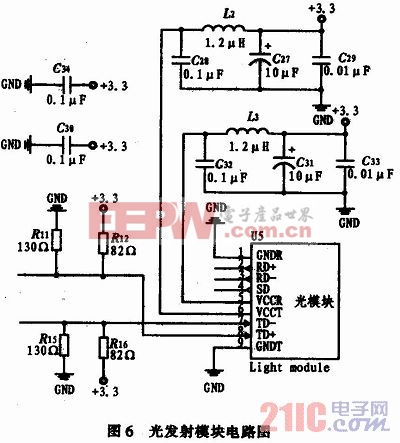

2. 4. 2 电/光模块

采用型号为HNMS-XEMC41XSC20,工作波长在T1310nm/R1550nm的单纤双向一体化收发模块,将电信号差分数据流转成光数据信号流,电路如图6所示。本文引用地址:https://www.eepw.com.cn/article/165897.htm

2.5 信号的接收及处理

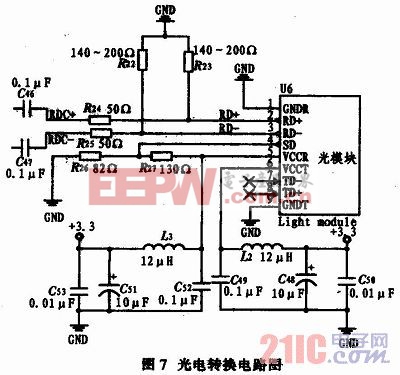

2.5.1 光/电转换模块

装置以单纤进行信号传输,光信号传输到接收装置后,需要还原为电信号,即差分电压数据流。采用型号为HNMS-XEMC41XSC20,工作波长在T1310 nm/R1550 nm的单纤双向一体化收发模块,将光信号转换为电信号。转换后的差分信号由RD+和RD-输出。电路如图7所示。

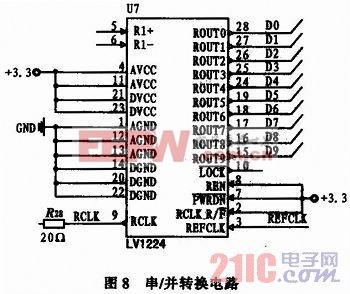

2. 5. 2 串并转换

装置采用与发送器中的串化器DS92LV1023相匹配的解串器DS92LV1224。发送器中的串化器将10位的并行数据转换为串行的差分数据流,因此在接收器中需用相应的解串器将串行差分数据流还原为并行数据。

DS92LV1224内部有锁相环,在接收数据流时可以根据数据的频率自行匹配接收时钟,外界只需为其提供参考时钟。此处参考时钟选为16MHz,由FPGA控制部分提供。芯片还匹配了与解串后的数据同步的时钟,以助于转换后的并行数据输出。参考时钟和数据输出时钟分别为REFCLK和RCLK引脚。为了保证视频信号的连续性和实时性,需避免芯片处于省电模式或高阻模式。因此PWRDN和REN需接高电平。RCLK-R/F接高电平,即选择时钟上升沿输出数据。

该组芯片有2种同步方式:快速同步和随机同步。快速同步是由串化器发送一组由连续的6个“1”和“0”组成的同步信号,解串器收到信号后锁定数据时钟,锁定完成之前LOCK保持高电平,同步完成后跳变为低电平。同步信号的发送是由串化器的SYNC1和SYNC2控制的,只要两者之一置高电平持续时间超过6个时钟周期,串化器就开始连续发送同步信号。快速同步具有快速准确的优点,但在长距离的信号传输中,光纤只传递数据,无法很好的传递串化器和解串器的SYNC和LOCK信号。因此采用随机同步方式。随机同步方式串化器不需发送同步信号,解串器直接对数据流进行锁定,实现同步,锁定丢失后,解串器会重新锁定时钟。将LOCK接到FPGA以进行实时控制。串/并转换电路如图8所示。

评论