SDRAM文件结构存储控制的FPGA实现

基于文件结构的存储方式便于对数据进行管理与操作,功能扩展容易。例如有些处理只对数据的帧头信息进行相关操作,基于文件结构的存储模式可以很方便地支持这种工作模式,只需对缓存介质的帧头区进行操作,而传统的设计则很难满足这种需求,因此新的设计极大地提高了系统的灵活性。

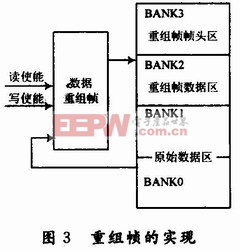

2.2 数据重组帧的实现

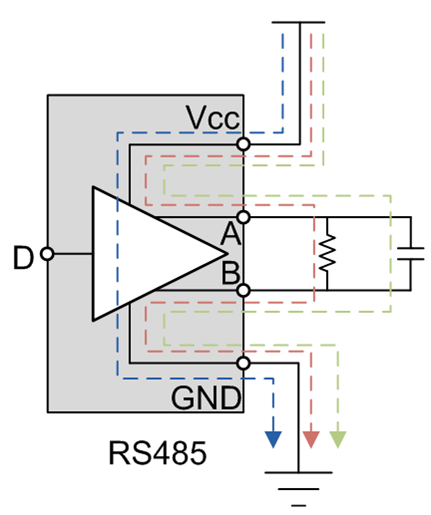

在设计上,用SDRAM的BANK0(BANK地址“00)和BANKl(BANK地址“01”)存储原始数据,BANK2(BANK地址“10”)存储要送往后端计算的数

据,BANK3(BANK地址“11”)存储数据的帧头信息。系统在接收到数据重组帧命令后,按照要求抽取,帧数,帧长和帧间隔从低BANK区读取原始数据送入数据重组帧模块形成新的数据帧结构,然后将新的数据帧结构按照文件结构存储到高BANK区中。其实现框图如图3所示。本文引用地址:https://www.eepw.com.cn/article/162810.htm

3 控制模块的结构化状态机设计

在系统架构上采用了结构化状态机的设计方法,通过分层有限状态机实现了主控状态机与具体操作控制状态机的分离,使设计结构清晰,划分合理。降低了设计的复杂性,同时使系统更具有通用性。

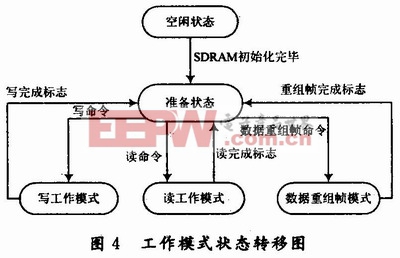

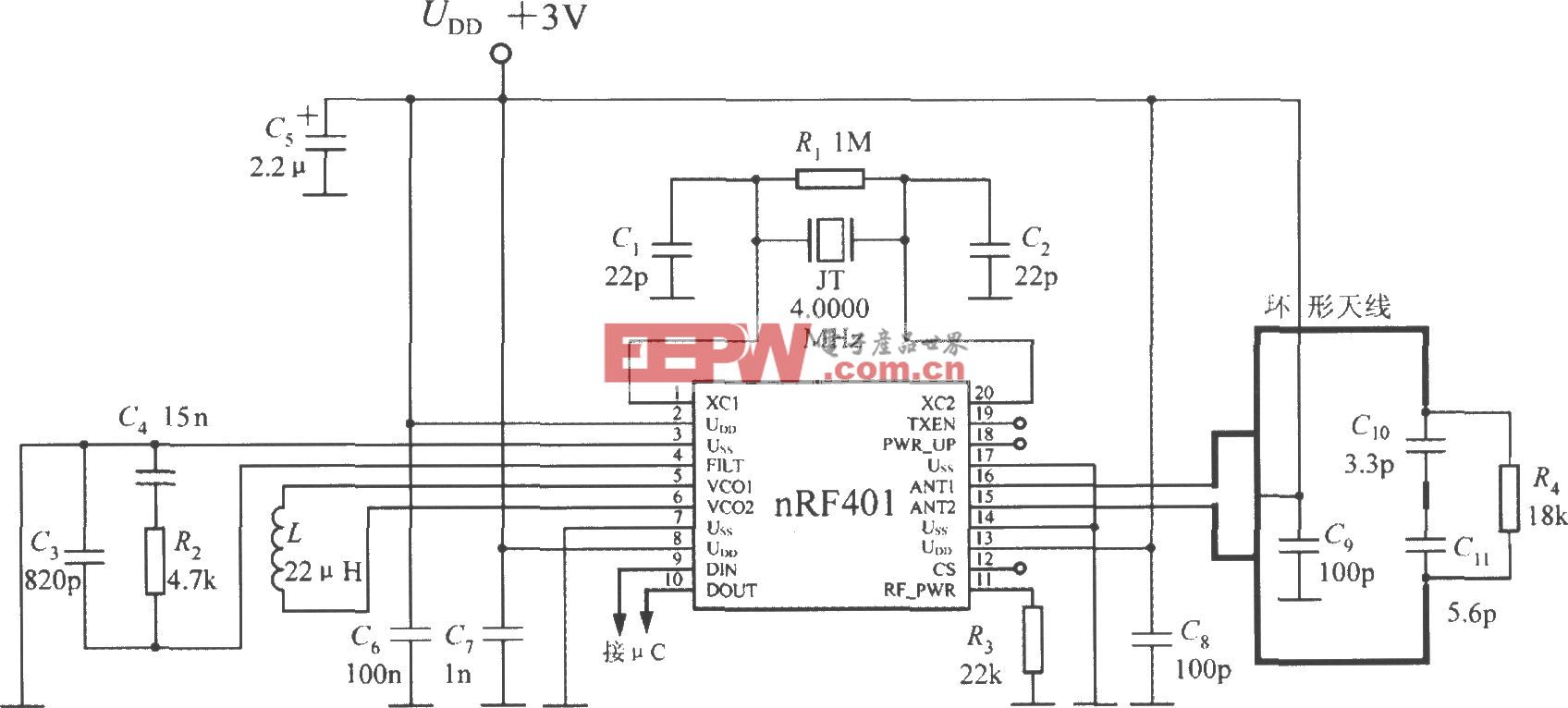

3.1 高层工作模式主控状态机设计

该缓存系统有3种工作模式:写模式,读模式和数据重组帧模式。其状态转移图如图4所示。

系统在空闲状态等待SDRAM初始化完成,当SDRAM完成初始化以后进入准备状态,表示系统可以接收命令,在收到写命令后进入写工作模式,低层写辅助控制模块激活,当完成写操作命令后产生一写完成标志信号,反馈回主控系统促使主控系统完成状态跳转回到准备状态等待下一次命令,收到读取命令后系统进入读工作模式,低层读辅助控制模块开始工作当完成读取操作后产生一读完成标志信号,反馈回主控系统使其回到准备状态等待命令,同样系统收到数据重组帧命令后进人数据重组帧模式,低层重组帧辅助控制模块开始工作完成重组帧任务后产生标志信号控制主控状态机再次回到准备状态,等待下一次命令。

这种结构化状态机的设计,层次划分合理清晰,工作模式的切换只在主控状态机中实现,各低层辅助控制模块仅仅实现其特定的功能,完全没有交互。因此这种设计可以很方便地进行功能扩展,以后系统要增加新的工作模式,只需再加入一个状态,并单独设计其辅助控制模块即可,无需对原有工作模式进行改动。同时,这种分层设计符合模块化设计的思想,降低了设计的复杂性,易于调试。

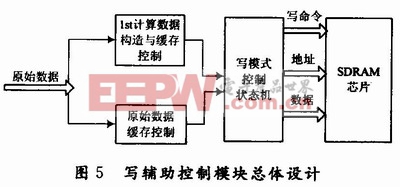

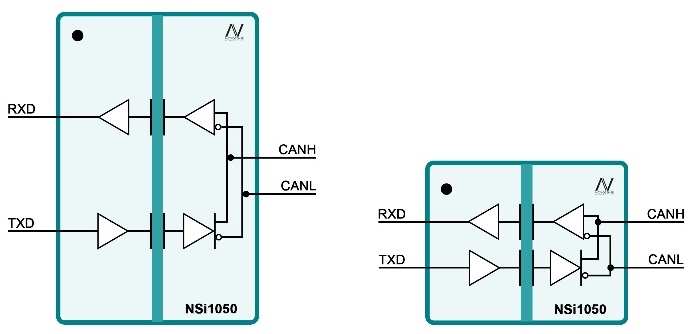

3.2 低层写辅助控制模块的设计

写辅助控制模块用来实现对原始数据和第1次计算数据基于文件结构的存储。为了提高系统效率,第1次计算所需的数据和原始数据同时存储。其总体设计框图如图5所示。

写辅助控制模块在主控状态机进入写工作模式时激活,通过将原始数据分为2路,一路进入原始数据缓存控制模块实现对原始数据的缓存,当原始数据的数据量积累到SDRAM一次突发写所需长度时,该控制模块发出写标志信号通知写模式控制状态机,写模式控制状态机响应写标志信号,向SDRAM驱动控制器发出写指令字控制SDRAM将原始数据写入SDRAM的原始数据区;另一路进入1st计算数据构造与缓存控制模块,该模块用来完成1st计算数据的帧头与数据的构造和缓存,当帧头构造完毕时,通知写模式控制状态机,将帧头(包含数据存储首地址信息)写入到SDRAM的帧头区中,同时当新数据量达到一次突发写入时,将新数据写入SDRAM的计算数据区中,直到将所有数据都写入到SDRAM的对应区内,写模式控制状态机发出写完成标志信号,反馈给高层主控状态机。

3.3 低层读辅助控制模块的设计

读辅助控制模块,接收读指令字,该指令字包括帧数、帧长和偏移地址。帧数表征着本次命令要从SDRAM中读取多少帧数据,帧长表示每帧数据要读取的长度(按采样点数算),偏移地址控制对数据的移位读操作。按照指令要求从SDRAM的高BANK区,读出数据送往后端。图6是其总体设计框图。

评论