SoC设计中的片上通信体系结构研究

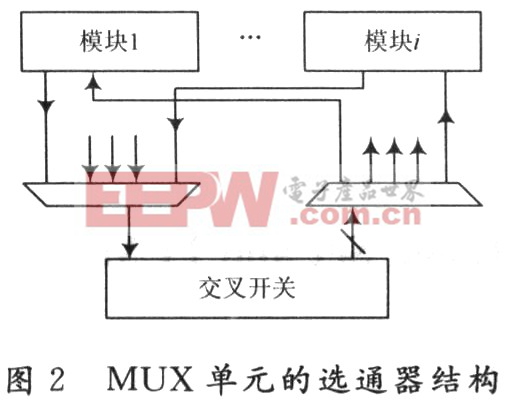

图1中,进行数据报文交换的是交叉开关。如果在SoC中仅有一个或两个DSP,该交叉开关可以有2M个端口;而如果存在一个处理器(DSP)阵列,则该交叉开关可以有2M+1个端口,以便于二维网格的扩展。图1中的MUX单元可以采用选通器,如图2所示。本文引用地址:https://www.eepw.com.cn/article/157785.htm

目前已经完成对仲裁器、接口单元和片上交叉开关进行Verilog的RTL代码编写,在Cadence的仿真环境下进行了功能验证。下一步将针对TSMC的180 nm低功耗标准单元库进行逻辑综合,在Cadence的仿真环境下得到面积、功耗和主频等性能参数,并完成对上述片上通信结构后端的设计和评估。

3 结 语

经验证,该片上通信的优化体系结构既保留了片上共享总线的面积小的优点,又具有片上网络的并行通信的优点。目前,具有优化体系结构的片上通信IP核,已经应用于实际的SoC设计中。将来,该研究结果在我国已发展或将要发展的高清晰度数字电视处理器SoC芯片、3G无线移动终端基带SoC芯片和其他SoC芯片的设计中,都会具有重要的实际应用意义。

评论