基于ADF4360-1的本振源设计

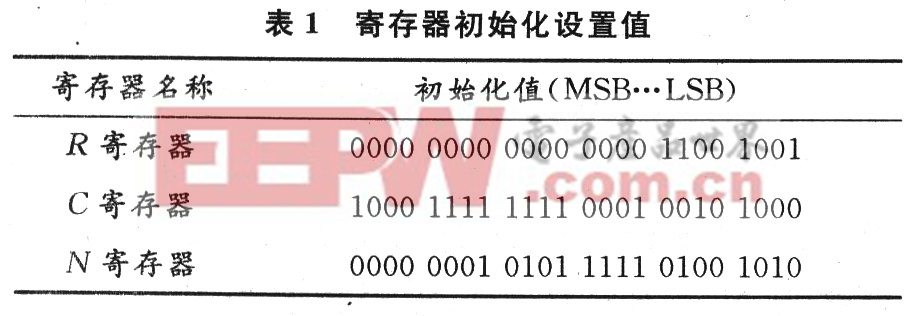

本电路设计中,ADF4360-1的PFD输入频率为200 kHz,因此参考时钟分频R=50。由公式fout=(B×P+A)×fref/R,可计算出N为11 250,双模前置分频器设置为P/(P+1)=32/33,计数器A设置为18,计数器B设置为351。根据ADF4360-1芯片资料,三个控制寄存器初始化设置为R寄存器0000C9H,C寄存器8FF128H,N寄存器015F4AH,如表1所示。本振源电路输出信号功率为-6 dB。本文引用地址:https://www.eepw.com.cn/article/157727.htm

2.2 环路滤波器电路设计

环路滤波器(LPF)具有低通特性,它主要是抑制鉴相器输出电压中的载频分量和高频噪声,降低由VCO控制电压的不纯而引起的寄生输出。更重要的是它对环路参数调整起着决定性的作用。

利用AD公司提供的专用设计与仿真工具软件ADI simPLL对图2结构形成的无源三阶滤波电路进行仿真、设计。依照软件提示,逐步设定各项参数,并选择芯片型号和环路滤波器形式,最后生成的电路如图3所示。

2.3 锁相环本振源电路设计

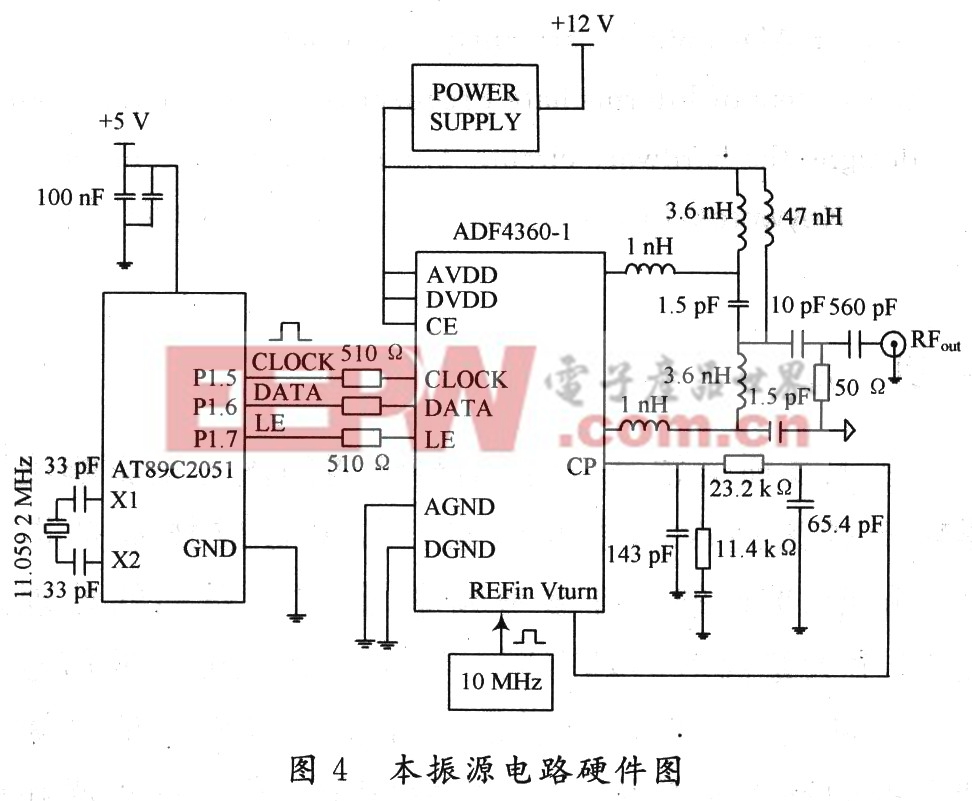

完整的硬件原理图如图4所示。

电源电路采用TPS76333和LM317T产生稳定的3.3 V电压供电。ADF4360-1的参考时钟输入引脚与晶振电路输出端相连,在内部VCO输入引脚VTUNE与内部电荷泵输出引脚CP之间接入三阶环路滤波电路。

核心芯片内部控制寄存器的初始化数值通过单片机控制写入,单片机采用ATMEL公司的AT89C2051。

评论